IN74ACT323 데이터 시트보기 (PDF) - Integral Corp.

부품명

상세내역

일치하는 목록

IN74ACT323 Datasheet PDF : 7 Pages

| |||

IN74ACT323

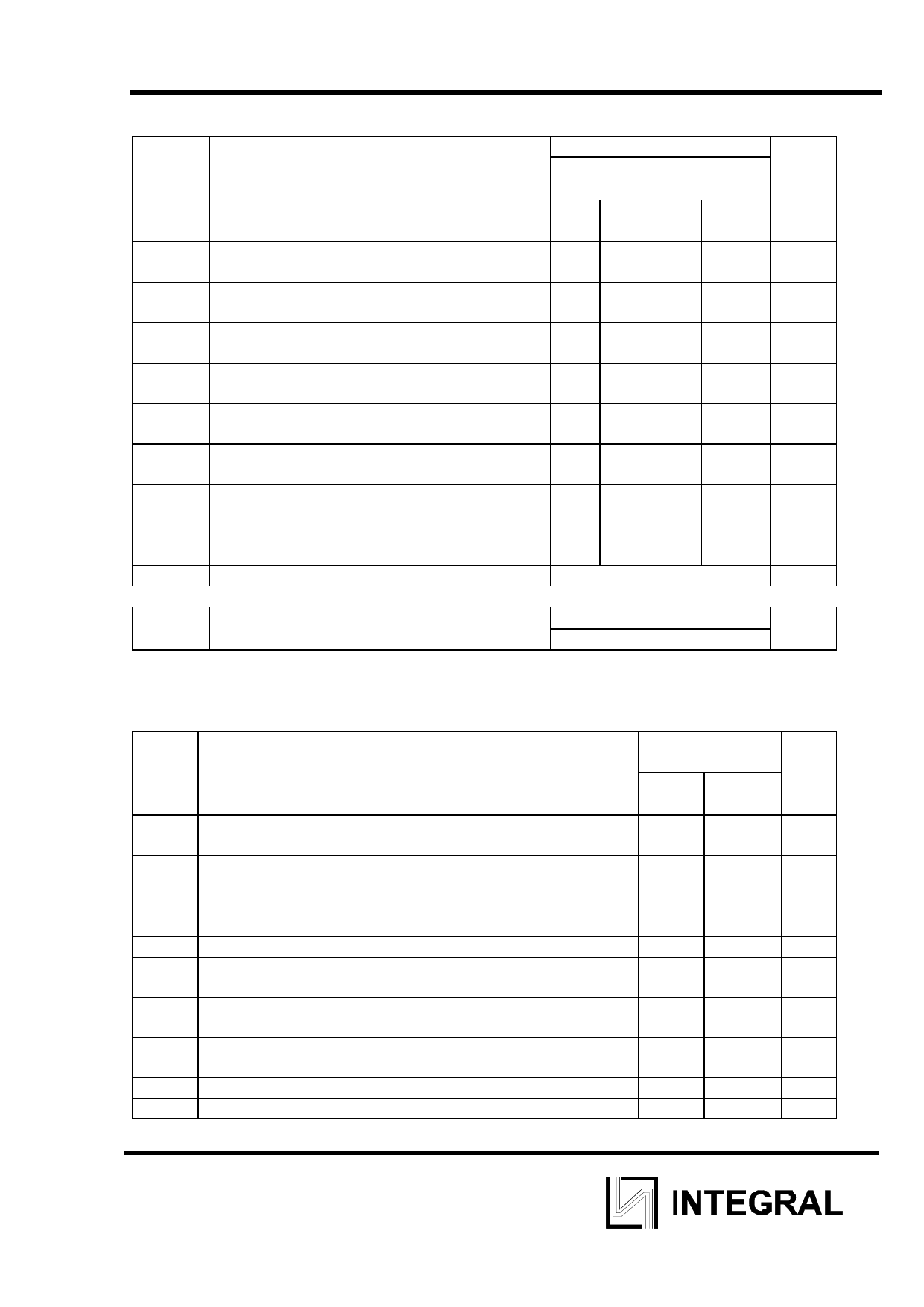

AC ELECTRICAL CHARACTERISTICS(VCC=5.0 V ± 10%, CL=50pF,Input tr=tf=3.0 ns)

Guaranteed Limits

Symbol

Parameter

25 °C

-40°C to

Unit

85°C

Min Max Min Max

fmax Maximum Clock Frequency (Figure 1)

120

110

MHz

tPLH Propagation Delay, Clock to QA’ or QH’ 5.0 12.5 4.0 14.0

ns

(Figure 1)

tPHL Propagation Delay, Clock to QA’ or QH’ 5.0 13.5 4.5 15.0

ns

(Figure 1)

tPLH Propagation Delay, Clock to QA thru QH 5.0 12.5 4.5 13.5

ns

(Figure 1)

tPHL Propagation Delay, Clock to QA thru QH 6.0 15.0 5.0 16.5

ns

(Figure 1)

tPZH Propagation Delay , OE1, OE2 to QA thru 3.5 11.0 3.0 12.5

ns

QH (Figure 3)

tPZL Propagation Delay , OE1, OE2 to QA thru 3.5 11.5 3.0 13.0

ns

QH (Figure 3)

tPHZ Propagation Delay , OE1, OE2 to QA thru 4.0 12.5 3.0 13.5

ns

QH (Figure 3)

tPLZ Propagation Delay , OE1, OE2 to QA thru 3.0 11.5 2.5 12.5

ns

QH (Figure 3)

CIN Maximum Input Capacitance

4.5

4.5

pF

CPD Power Dissipation Capacitance

Typical @25°C,VCC=5.0 V

170

pF

TIMING REQUIREMENTS(VCC=5.0 V ± 10%, CL=50pF, Input tr=tf=3.0 ns)

Guaranteed

Limits

Symb

Parameter

25 °C -40°C Unit

ol

to 85°C

tsu Minimum Setup Time, Mode Select S1 or S2 to Clock 5.0

5.0

ns

(Figure 4)

tsu Minimum Setup Time, Data Inputs PA thru PH to Clock 4.0

4.5

ns

(Figure 4)

tsu Minimum Setup Time, Data Inputs SA, SH to Clock 4.5

5.0

ns

(Figure 4)

tsu Minimum Setup Time, Reset to Clock (Figure 2)

2.5

2.5

ns

th Minimum Hold Time, Clock to Mode Select S1 or S2 1.5

1.5

ns

(Figure 4)

th Minimum Hold Time, Clock to Data Inputs PA thru PH 1.0

1.0

ns

(Figure 4)

th Minimum Hold Time, Clock to Data Inputs SA, SH 1.0

1.0

ns

(Figure 4)

th Minimum Hold Time, Clock to Reset (Figure 2)

1.0

1.0

ns

tw Minimum Pulse Width, Clock (Figure 1)

4.0

4.5

ns

4