IDT54FCT162823ATE 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

IDT54FCT162823ATE Datasheet PDF : 9 Pages

| |||

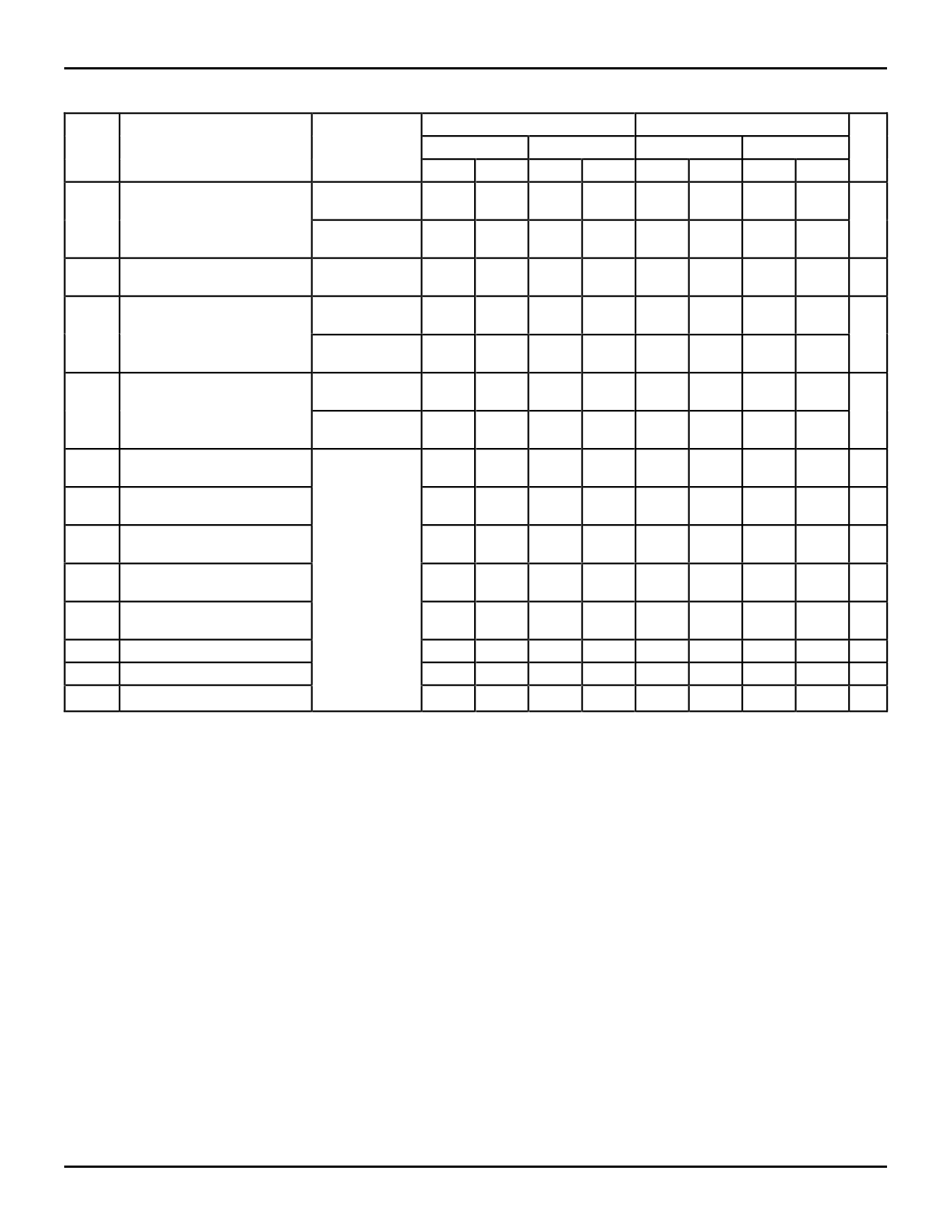

IDT54/74FCT16823AT/BT/CT/ET, 162823AT/BT/CT/ET

FAST CMOS 18-BIT REGISTER

MILITARY AND COMMERCIAL TEMPERATURE RANGES

SWITCHING CHARACTERISTICS OVER OPERATING RANGE

FCT16823CT/162823CT

FCT16823ET/162823ET

Symbol

Parameter

Condition(1)

Com'l.

Min.(2) Max.

Mil.

Min.(2) Max.

Com'l.

Min.(2) Max.

Mil.

Min.(2) Max.

Unit

tPLH Propagation Delay

CL = 50pF

1.5 6.0 1.5 7.0 1.5 4.4

—

— ns

tPHL xCLK to xQx

RL = 500Ω

CL = 300pF(5) 1.5 12.5 1.5 13.5 1.5

8.0

—

—

RL = 500Ω

tPHL Propagation Delay

CL = 50pF

1.5 8.0 1.5 8.5 1.5 4.4

—

— ns

xCLR to xQx

RL = 500Ω

tPZH Output Enable Time

CL = 50pF

1.5 7.0 1.5 8.0 1.5 4.4

—

— ns

tPZL xOE to xQx

RL = 500Ω

CL = 300pF(5) 1.5 12.5 1.5 13.5 1.5

9.0

—

—

tPHZ Output Disable Time

RL = 500Ω

CL = 5pF(5)

1.5 6.2 1.5 6.2 1.5 3.6

—

— ns

tPLZ xOE to xQx

RL = 500Ω

CL = 50pF

1.5 6.5 1.5 6.5 1.5 3.6

—

—

RL = 500Ω

tSU Set-up Time HIGH or LOW

CL = 50pF

3.0

—

3.0

—

1.5

—

—

— ns

xDx to xCLK

RL = 500Ω

tH Hold Time HIGH or LOW

1.5

—

1.5

—

0.0

—

—

— ns

xDx to xCLK

tSU Set-up Time HIGH or LOW

3.0

—

3.0

—

2.5

—

—

— ns

xCLKEN to xCLK

tH Hold Time HIGH or LOW

0

—

0

—

0.0

—

—

— ns

xCLKEN to xCLK

tW xCLK Pulse Width

6.0

—

6.0

— 3.0(4) —

—

— ns

HIGH or LOW

tW xCLR Pulse Width LOW

6.0

—

6.0

— 3.0(4) —

—

— ns

tREM Recovery Time xCLR to xCLK

tSK(o) Output Skew(3)

6.0

—

6.0

—

3.0

—

—

—

0.5

—

0.5

—

0.5

—

— ns

— ns

NOTES:

1. See test circuit and waveforms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

3. Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.

4. This limit is guaranteed but not tested.

5. This condition is guaranteed but not tested.

2772 tbl 10

5.16

7