ICS9250-12 데이터 시트보기 (PDF) - Integrated Circuit Systems

부품명

상세내역

일치하는 목록

ICS9250-12 Datasheet PDF : 12 Pages

| |||

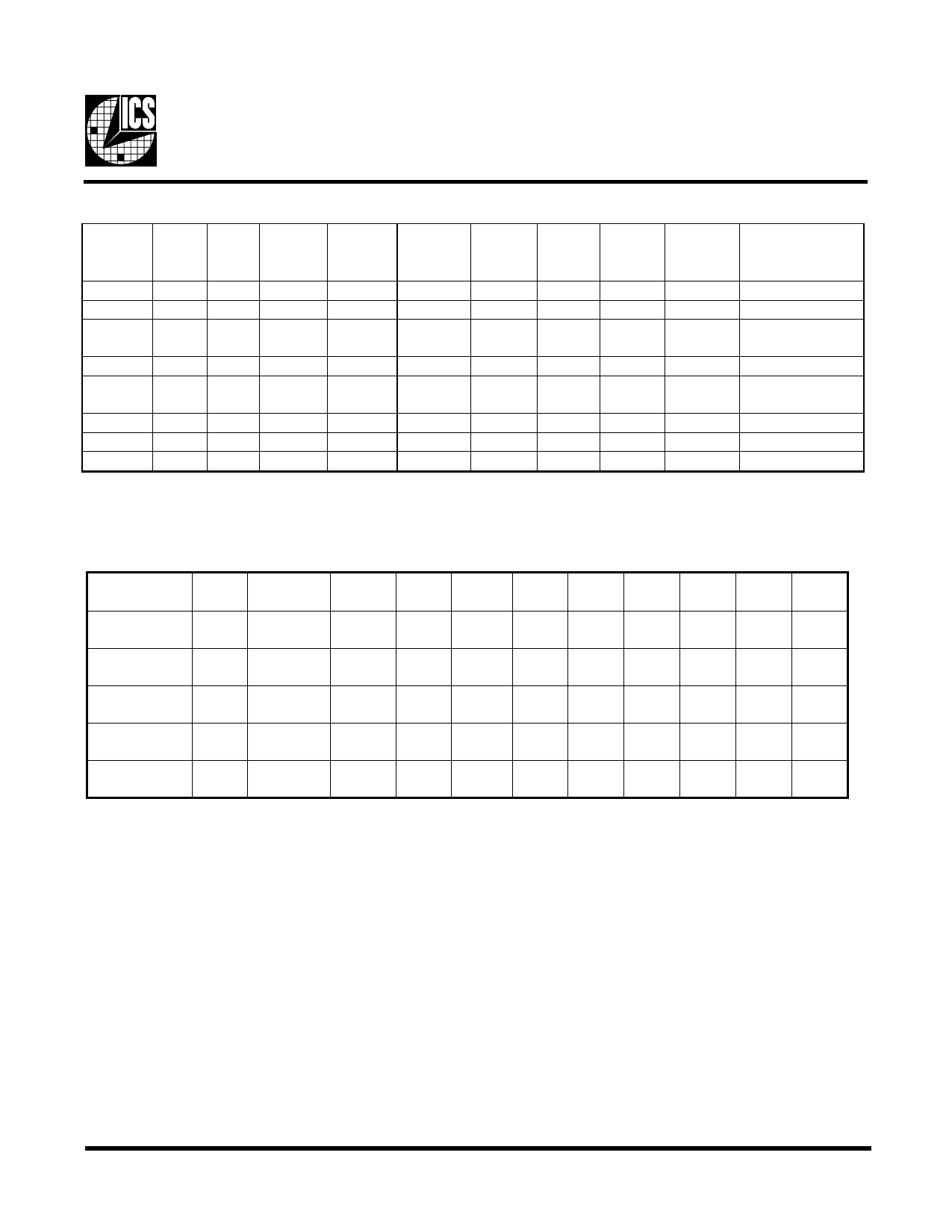

ICS9250-12

Frequency Select:

SEL

133/100- SEL1 SEL0

#

CPU

MHz

0

0

0 Hi-Z

0

0

1 N/A

CPU/2

MHz

Hi-Z

N/A

3V66

MHz

Hi-Z

N/A

PCI

MHz

Hi-Z

N/A

48

MHz

Hi-Z

N/A

REF

MHz

Hi-Z

N/A

IOAPIC

MHz

Hi-Z

N/A

0

1 0 100

50

66

33 Hi-Z 14.318 16.67

0

1

1 100

50

66

33

48 14.318 16.67

1

0

0

TCLK/2 TCLK/4

TCLK/4

TCLK/8

TCLK/-

2

TCLK

TCLK/16

1

0

1 N/A N/A N/A N/A N/A N/A N/A

1

1 0 133

66

66

33 Hi-Z 14.318 16.67

1

1

1 133

66

66

33

48 14.318 16.67

Note:

1. TCLK is a test clock driven on the x1 input during test mode.

Comments

Tri-state

Reserved

48MHz PLL

disabled

Test mode (1)

Reserved

ICS9250-12 Power Management Features:

CPU_STOP#

X

PD# PCI_STOP# CPUCLK CPU/2 IOAPIC 3V66

0

X

LOW LOW LOW LOW

PCI

PCI_F

REF.

48MHz

Osc

LOW LOW LOW OFF

VCOs

OFF

0

1

0

LOW ON

ON LOW LOW ON

ON ON

ON

0

1

1

LOW ON

ON LOW ON

ON

ON ON

ON

1

1

0

ON

ON

ON

ON LOW ON

ON ON

ON

1

1

1

ON

ON

ON

ON ON

ON

ON ON

ON

Note:

1. LOW means outputs held static LOW as per latency requirement next page.

2. On means active.

3. PD# pulled Low, impacts all outputs including REF and 48 MHz outputs.

4. All 3V66 as well as all CPLU clocks should stop cleanly when CPU_STOP# is pulled LOW.

5. CPU/2, IOAPIC, REF, 48 MHz signals are not controlled by the CPU_STOP# functionality and are enabled all in all conditions

except PD# = LOW

Power Groups:

VDDREF, GNDREF = REF, X1, X2

GNDPCI, VDDPCI = PCICLK

VDD66, GND66 = 3V66

VDD48, GND48 = 48MHz

VDDCOR, GNDCOR = PLL Core

VDDLCPU/2 , GNDLCPU/2 = CPU/2

VDDLIOAPIC, GNDIOAPIC = IOAPIC

3