HD74LV166ATELL(2004) 데이터 시트보기 (PDF) - Renesas Electronics

부품명

상세내역

일치하는 목록

HD74LV166ATELL Datasheet PDF : 10 Pages

| |||

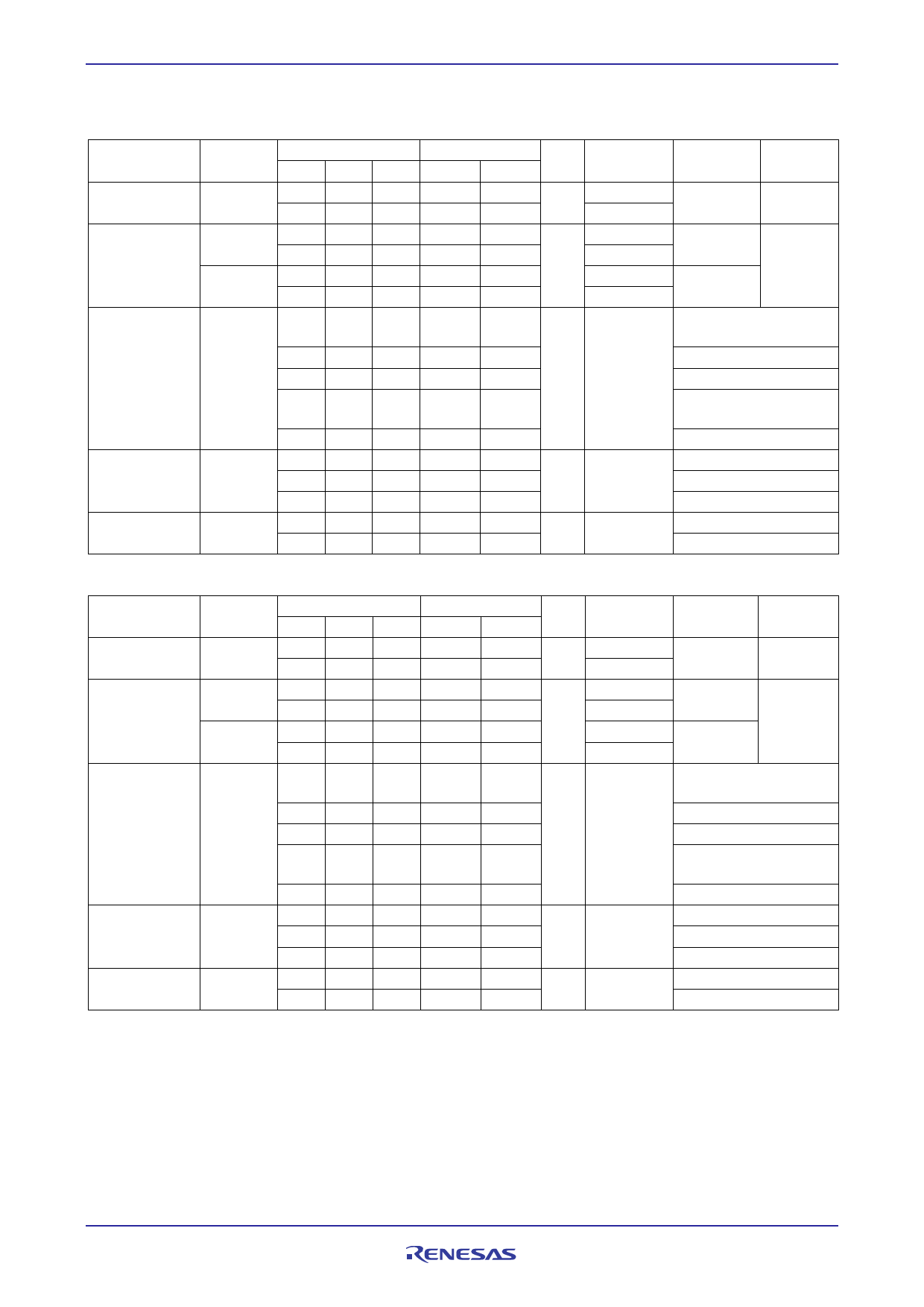

HD74LV166A

Switching Characteristics

Item

Maximum clock

frequency

Propagation

delay time

Symbol

fmax

tPLH/tPHL

tPHL

Setup time

tsu

Hold time

th

Pulse width

tw

Ta = 25°C

Min Typ

50 80

40 65

— 12.2

— 15.3

— 10.8

— 14.2

6.0 —

7.0 —

6.5 —

7.0 —

8.5 —

–0.5 —

–0.5 —

–0.5 —

8.0 —

8.5 —

Max

—

—

19.8

23.3

16.0

19.5

—

—

—

—

—

—

—

—

—

—

Ta = –40 to 85°C

Min

Max

45

—

35

—

1.0

22.0

1.0

26.0

1.0

18.0

1.0

22.0

7.0

—

7.0

—

8.5

—

8.5

—

9.5

—

0.0

—

0.0

—

0.0

—

9.0

—

9.0

—

Unit

MHz

ns

ns

ns

ns

Test

Conditions

CL = 15 pF

CL = 50 pF

CL = 15 pF

CL = 50 pF

CL = 15 pF

CL = 50 pF

FROM

(Input)

VCC = 2.5 ± 0.2 V

TO

(Output)

CLK

QH

CLR

CLR inactive before

CLK ↑

CLK INH before CLK ↑

Data before CLK ↑

SH/LD high before CLK

↑

SER before CLK ↑

PAR data after SH/LD ↑

SER data after CLK ↑

SH/LD high after CLK ↑

CLR low

CLK H or L

Item

Maximum clock

frequency

Propagation

delay time

Symbol

fmax

tPLH/tPHL

tPHL

Setup time

tsu

Hold time

th

Pulse width

tw

Ta = 25°C

Ta = –40 to 85°C

Test

VCC = 3.3 ± 0.3 V

FROM

TO

Min Typ Max Min

Max

Unit Conditions (Input)

(Output)

65 115 — 55

60 90 — 50

— 8.6 15.4 1.0

— 10.9 18.9 1.0

— 7.9 12.5 1.0

— 10.4 16.3 1.0

4.0 — — 4.0

—

—

18.0

21.5

15.0

18.5

—

MHz

ns

ns

CL = 15 pF

CL = 50 pF

CL = 15 pF

CL = 50 pF

CL = 15 pF

CL = 50 pF

CLK

QH

CLR

CLR inactive before

CLK ↑

5.0 — — 5.0

—

CLK INH before CLK ↑

5.0 — — 6.0

—

Data before CLK ↑

5.0 — — 6.0

—

SH/LD high before CLK

↑

5.0 — — 6.0

—

SER before CLK ↑

0.0 — — 0.0

—

ns

PAR data after SH/LD ↑

0.0 — — 0.0

—

SER data after CLK ↑

0.0 — — 0.0

—

SH/LD high after CLK ↑

6.0 — — 7.0

—

ns

CLR low

6.0 — — 7.0

—

CLK H or L

Rev.3.00 Jun. 04, 2004 page 6 of 9