DS2165 데이터 시트보기 (PDF) - Dallas Semiconductor -> Maxim Integrated

부품명

상세내역

일치하는 목록

DS2165 Datasheet PDF : 17 Pages

| |||

DS2165Q

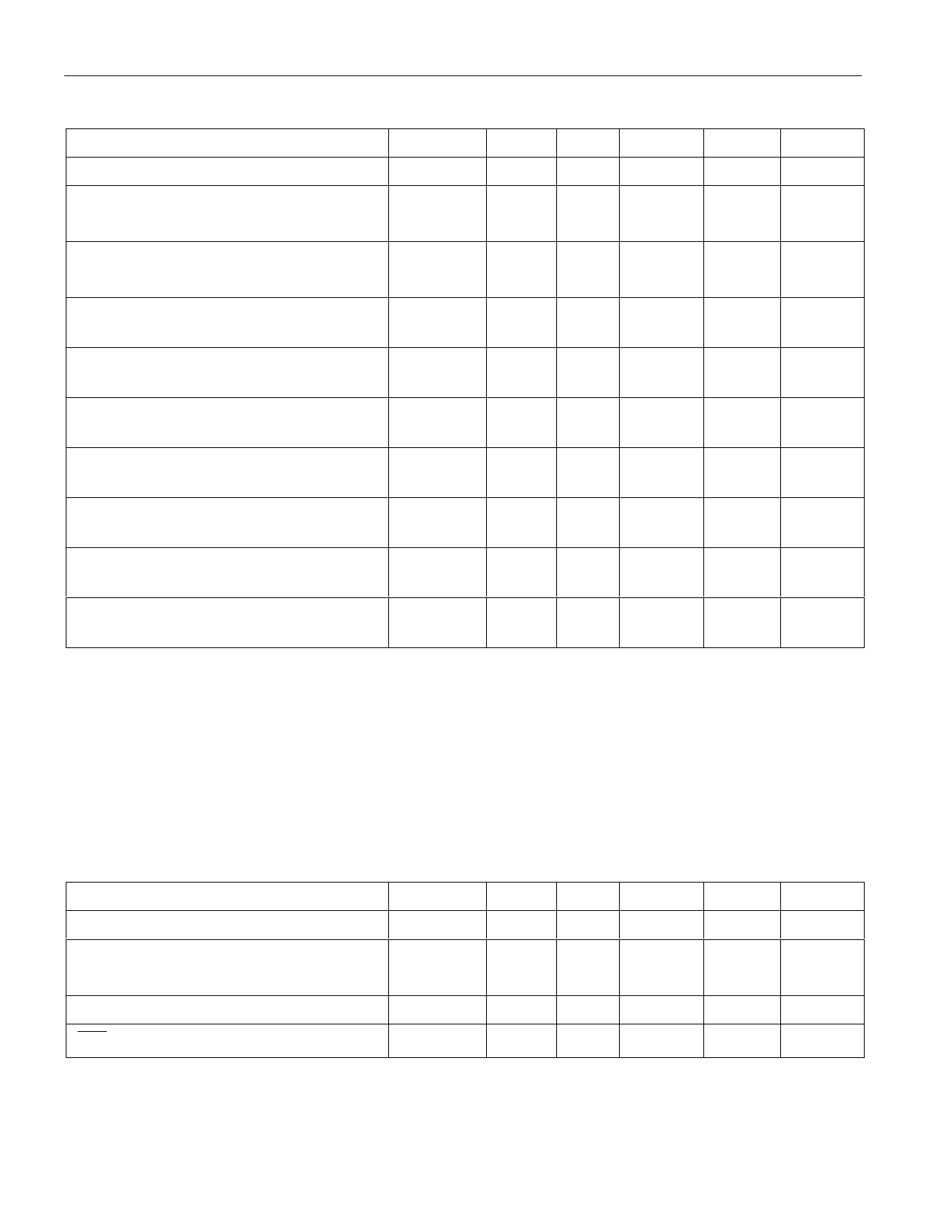

PCM INTERFACE, AC ELECTRICAL CHARACTERISTICS

(VDD = 5V ±10%, TA = 0°C to +70°C; VDD = 3.0V + 20% - 10% for DS2165QL)

PARAMETER

SYMBOL MIN TYP MAX UNITS NOTES

CLKX, CLKY Period

tPXY

244

3906

ns

1

CLKX, CLKY Pulse Width

tWXYL

100

ns

tWXYH

CLKX, CLKY Rise Fall Times

tRXY

tFXY

10

20

ns

Hold Time from CLKX, CLKY to FSX,

FSY

tHOLD

0

ns

2

Setup Time from FSX, FSY High to

CLKX, CLKY Low

tSF

50

ns

2

Hold Time from CLKX, CLKY Low to

FSX, FSY Low

tHF

100

ns

2

Setup Time for XIN, YIN to CLKX,

CLKY Low

tSD

50

ns

2

Hold Time for XIN, YIN to CLKX,

CLKY Low

tHD

50

ns

2

Delay Time from CLKX, CLKY to

Valid XOUT, YOUT

tDXYO

10

150

ns

3

Delay Time from CLKX, CLKY to

XOUT, YOUT Tri-stated

tDXYZ

20

150

ns 2, 3, 4

NOTES:

1) Maximum width of FSX and FSY is one CLKX or CLKY period (except for signaling frames).

Maximum operating frequency is guaranteed by design and is not a tested parameter.

2) Measured at VIH = 2.0V, VIL = 0.8V, and 10ns maximum rise and fall times.

3) Load = 150pF + 2 LSTTL loads.

4) For LSB of PCM or ADPCM byte.

MASTER CLOCK/RESET, AC ELECTRICAL CHARACTERISTICS

(VDD = 5V ±10%, TA = 0°C to +70°C; VDD = 3.0V + 20% - 10% for DS2165QL)

PARAMETER

SYMBOL MIN TYP MAX UNITS NOTES

MCLK Period

tPM

100

ns

1

MCLK Pulse Width

tWMH,

45 50

55

ns

tWML

MCLK Rise/Fall Times

tRM, tFM

10

ns

RST Pulse Width

tRST

1

ms

NOTES:

1) MCLK = 10MHz ±500ppm

14 of 17