ADT7517ARQ-REEL 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

ADT7517ARQ-REEL

ADT7517ARQ-REEL Datasheet PDF : 44 Pages

| |||

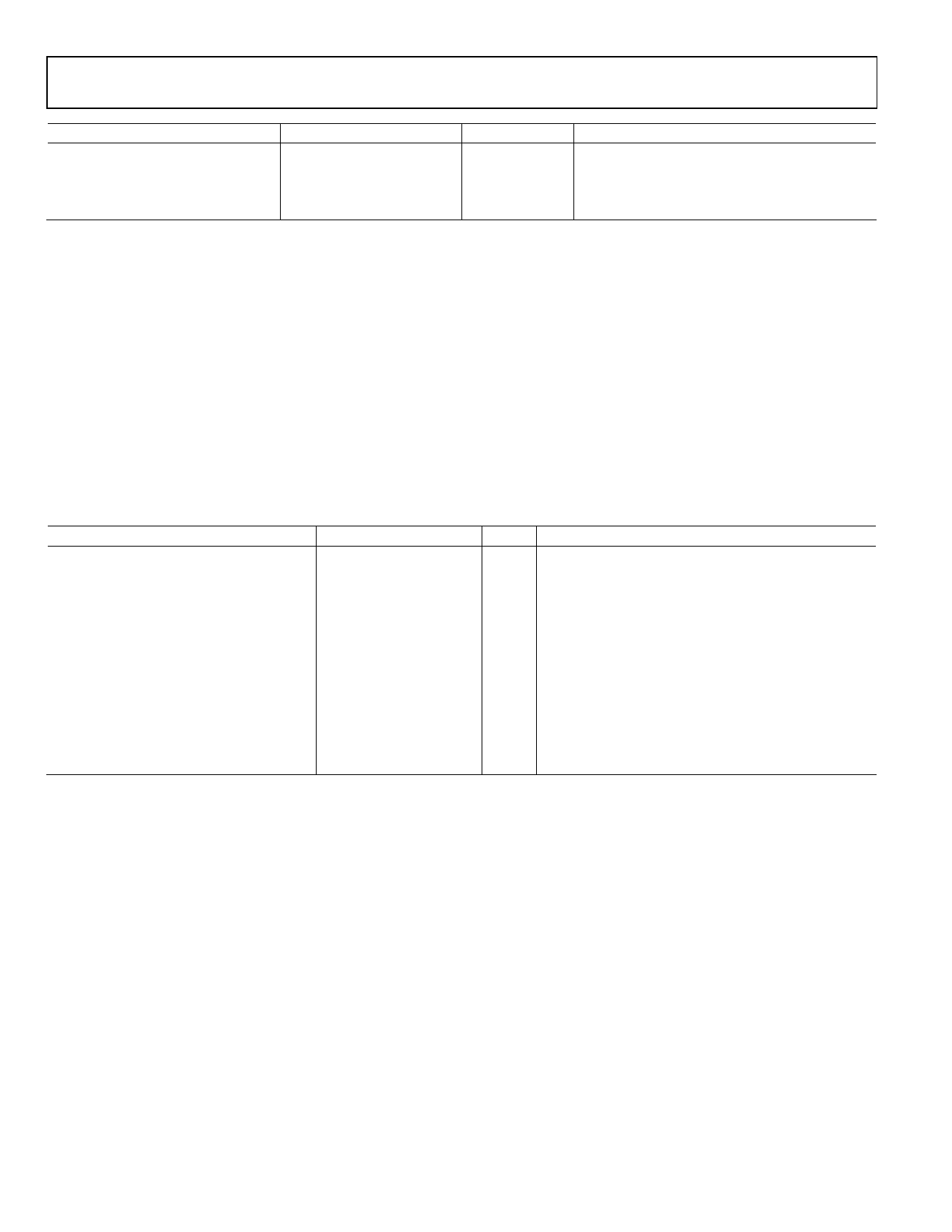

ADT7516/ADT7517/ADT7519

Parameter1

IDD (Power-Down Mode)

Power Dissipation

Min Typ Max

Unit

10

μA

10

μA

10

mW

33

μW

Conditions/Comments

VDD = 3.3 V, VIH = VDD, and VIL = GND

VDD = 5 V, VIH = VDD, and VIL = GND

VDD = 3.3 V, normal mode

VDD = 3.3 V, shutdown mode

1 See the Terminology section.

2 DC specifications are tested with the outputs unloaded.

3 Linearity is tested using a reduced code range: ADT7516 (Code 115 to 4095); ADT7517 (Code 28 to 1023); ADT7519 (Code 8 to 255).

4 Guaranteed by design and characterization, not production tested.

5 Round robin is the continuous sequential measurement of the following channels: VDD, internal temperature, external temperature (AIN1, AIN2), AIN3, and AIN4.

6 For the amplifier output to reach its minimum voltage, the offset error must be negative. For the amplifier output to reach its maximum voltage (VREF = VDD), the offset

plus gain error must be positive.

7 The SDA and SCL timing is measured with the input filters turned on to meet the fast mode I2C specification. Switching off the input filters improves the transfer rate

but has a negative effect on the EMC behavior of the part.

8 Guaranteed by design, not production tested. All I2C timing specifications are for fast mode operation but the interface is still capable of handling the slower standard

rate specifications.

9 The interface is also capable of handling the I2C standard mode rise time specification of 1000 ns.

10 All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD), and timed from a voltage level of 1.6 V.

11 Measured with the load circuit shown in Figure 4.

12 The IDD specification is valid for all DAC codes and full-scale analog input voltages. Interface inactive. All DACs and ADCs active. Load currents excluded.

DAC AC CHARACTERISTICS

VDD = 2.7 V to 5.5 V, RL = 4.7 kΩ to GND, CL = 200 pF to GND, 4.7 kΩ to VDD, all specifications TMIN to TMAX, unless otherwise noted.

Table 2.

Parameter1, 2

Output Voltage Settling Time

ADT7519

ADT7517

ADT7516

Slew Rate

Major-Code Change Glitch Energy

Digital Feedthrough

Digital Crosstalk

Analog Crosstalk

DAC-to-DAC Crosstalk

Multiplying Bandwidth

Total Harmonic Distortion

Min Typ3

6

7

8

0.7

12

0.5

1

0.5

3

200

–70

Max Unit Conditions/Comments

VREF = VDD = 5 V

8

μs

1/4 scale to 3/4 scale change (0x40 to 0xC0)

9

μs

1/4 scale to 3/4 scale change (0x100 to 0x300)

10

μs

1/4 scale to 3/4 scale change (0x400 to 0xC00)

V/μs

nV-s 1 LSB change around major carry

nV-s

nV-s

nV-s

nV-s

kHz VREF = 2 V ±0.1 V p-p

dB

VREF = 2.5 V ±0.1 V p-p; frequency = 10 kHz

1 See the Terminology section.

2 Guaranteed by design and characterization, not production tested.

3 At 25°C.

Rev. B | Page 6 of 44