ADT7517(RevA) 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

ADT7517

(Rev.:RevA)

(Rev.:RevA)

ADT7517 Datasheet PDF : 44 Pages

| |||

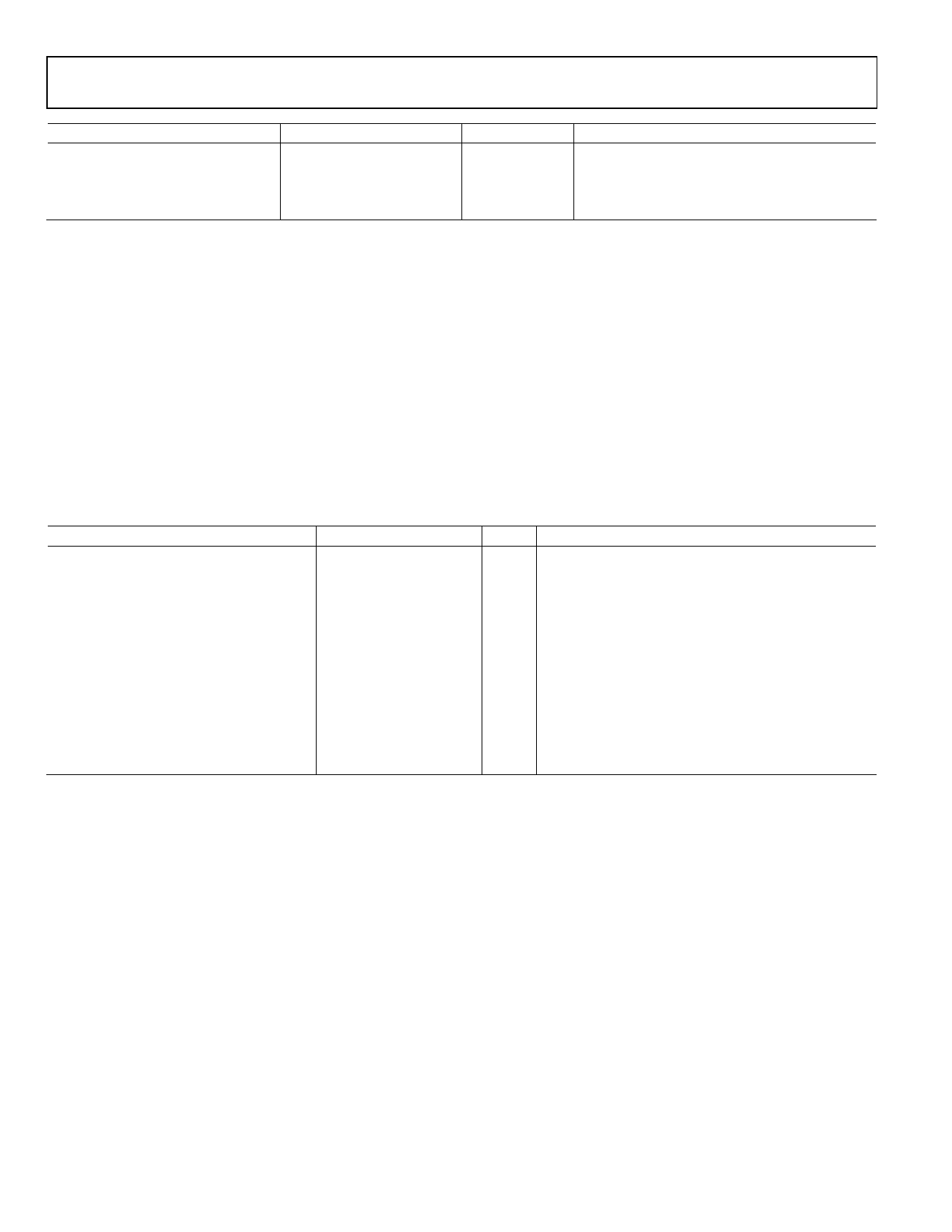

ADT7516/ADT7517/ADT7519

Parameter1

POWER REQUIREMENTS

VDD

VDD Settling Time

IDD (Normal Mode)11

IDD (Power-Down Mode)

Power Dissipation

Min Typ Max

Unit

2.7

5.5

V

50

ms

3

mA

2.2

3

mA

10

µA

10

µA

10

mW

33

µW

Conditions/Comments

VDD settles to within 10% of its final voltage level.

VDD = 3.3 V, VIH = VDD, and VIL = GND.

VDD = 5 V, VIH = VDD, and VIL = GND.

VDD = 3.3 V, VIH = VDD, and VIL = GND.

VDD = 5 V, VIH = VDD, and VIL = GND.

VDD = 3.3 V. Normal mode.

VDD = 3.3 V. Shutdown mode.

1 See the Terminology section.

2 DC specifications are tested with the outputs unloaded.

3 Linearity is tested using a reduced code range: ADT7516 (Code 115 to 4095); ADT7517 (Code 28 to 1023); ADT7519 (Code 8 to 255).

4 Guaranteed by design and characterization, not production tested.

5 Round robin is the continuous sequential measurement of the following channels: VDD, internal temperature, external temperature (AIN1, AIN2), AIN3, and AIN4.

6 For the amplifier output to reach its minimum voltage, the offset error must be negative. For the amplifier output to reach its maximum voltage (VREF = VDD), the offset

plus gain error must be positive.

7 The SDA and SCL timing is measured with the input filters turned on to meet the fast-mode I2C specification. Switching off the input filters improves the transfer rate

but has a negative effect on the EMC behavior of the part.

8 Guaranteed by design, not production tested.

9 All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD), and timed from a voltage level of 1.6 V.

10 Measured with the load circuit shown in Figure 4.

11 The IDD specification is valid for all DAC codes and full-scale analog input voltages. Interface inactive. All DACs and ADCs active. Load currents excluded.

DAC AC CHARACTERISTICS

Table 2. VDD = 2.7 V to 5.5 V, RL = 4.7 kΩ to GND; CL = 200 pF to GND; 4.7 kΩ to VDD; all specifications TMIN to TMAX, unless

otherwise noted.

Parameter1, 2

Min Typ3 Max Unit Conditions/Comments

Output Voltage Settling Time

VREF = VDD = 5 V.

ADT7519

6

8

µs

1/4 scale to 3/4 scale change (40h to C0h).

ADT7517

7

9

µs

1/4 scale to 3/4 scale change (100h to 300h).

ADT7516

8

10

µs

1/4 scale to 3/4 scale change (400h to C00h).

Slew Rate

0.7

V/µs

Major-Code Change Glitch Energy

12

nV-s 1 LSB change around major carry.

Digital Feedthrough

0.5

nV-s

Digital Crosstalk

1

nV-s

Analog Crosstalk

0.5

nV-s

DAC-to-DAC Crosstalk

3

nV-s

Multiplying Bandwidth

200

kHz VREF = 2 V ±0.1 V p-p.

Total Harmonic Distortion

–70

dB

VREF = 2.5 V ±0.1 V p-p. Frequency = 10 kHz.

1 See Terminology section.

2 Guaranteed by design and characterization, not production tested.

3 @ 25°C.

t1

SCL

t4

t2

t5

SDA

DATA IN

t3

SDA

DATA OUT

t6

Figure 2. I2C Bus Timing Diagram

Rev. A | Page 6 of 44