AD7691 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD7691 Datasheet PDF : 29 Pages

| |||

Data Sheet

AD7691

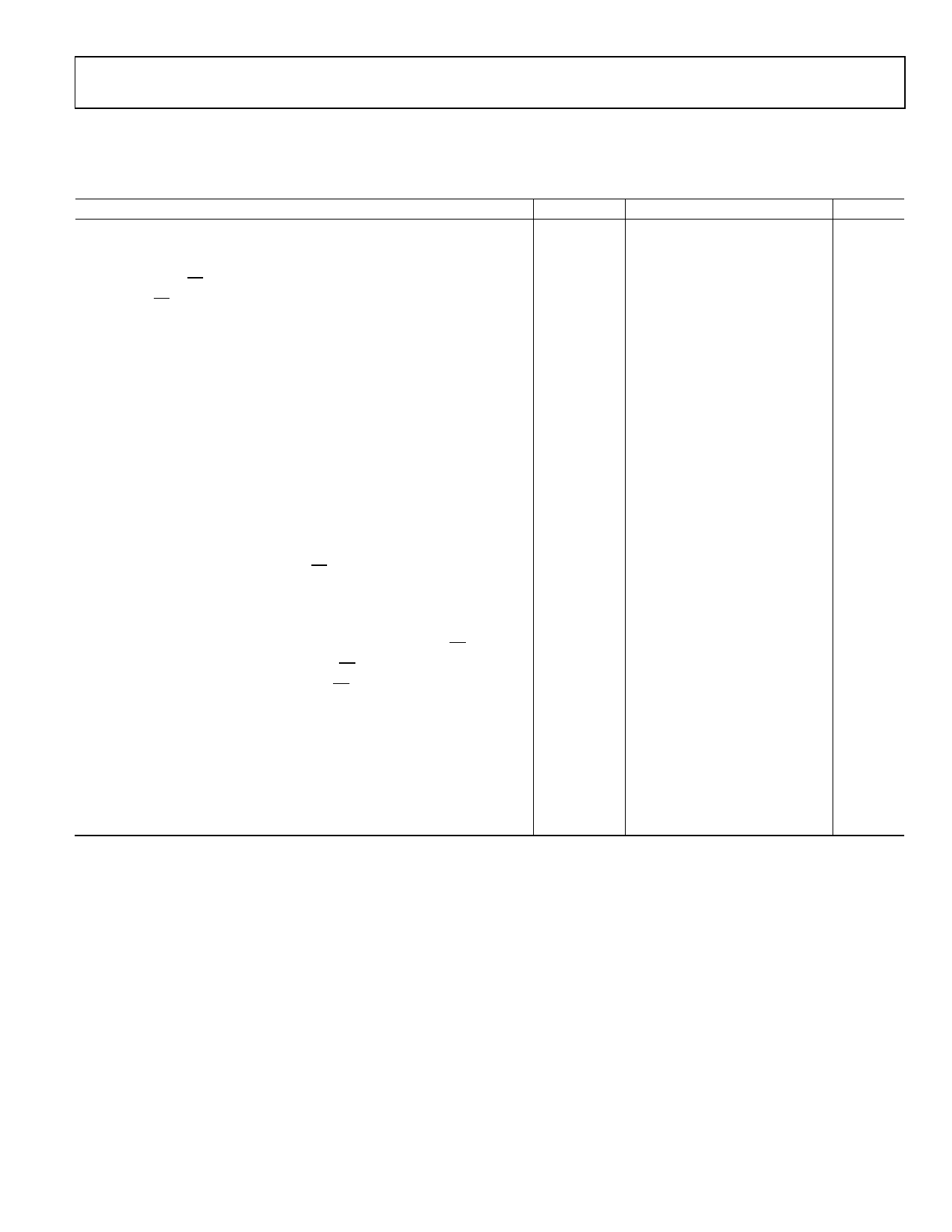

TIMING SPECIFICATIONS

VDD = 4.5 V to 5.25 V, VIO = 2.3 V to VDD, VREF = VDD, all specifications TMIN to TMAX, unless otherwise noted.1

Table 4.

Parameter

Symbol

Min

Typ

Max

Unit

Conversion Time: CNV Rising Edge to Data Available

tCONV

0.5

2.2

µs

Acquisition Time

tACQ

1.8

µs

Time Between Conversions

tCYC

4

µs

CNV Pulse Width (CS Mode)

tCNVH

10

ns

SCK Period (CS Mode)

tSCK

15

ns

SCK Period (Chain Mode)

tSCK

VIO Above 4.5 V

17

ns

VIO Above 3 V

18

ns

VIO Above 2.7 V

19

ns

VIO Above 2.3 V

20

ns

SCK Low Time

tSCKL

7

ns

SCK High Time

tSCKH

7

ns

SCK Falling Edge to Data Remains Valid

tHSDO

4

ns

SCK Falling Edge to Data Valid Delay

tDSDO

VIO Above 4.5 V

14

ns

VIO Above 3 V

15

ns

VIO Above 2.7 V

16

ns

VIO Above 2.3 V

17

ns

CNV or SDI Low to SDO D17 MSB Valid (CS Mode)

tEN

VIO Above 4.5 V

15

ns

VIO Above 2.7 V

18

ns

VIO Above 2.3 V

22

ns

CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode)

tDIS

25

ns

SDI Valid Setup Time from CNV Rising Edge (CS Mode)

tSSDICNV

15

ns

SDI Valid Hold Time from CNV Rising Edge (CS Mode)

tHSDICNV

0

ns

SCK Valid Setup Time from CNV Rising Edge (Chain Mode)

tSSCKCNV

5

ns

SCK Valid Hold Time from CNV Rising Edge (Chain Mode)

tHSCKCNV

10

ns

SDI Valid Setup Time from SCK Falling Edge (Chain Mode)

tSSDISCK

3

ns

SDI Valid Hold Time from SCK Falling Edge (Chain Mode)

tHSDISCK

4

ns

SDI High to SDO High (Chain Mode with Busy Indicator)

tDSDOSDI

VIO Above 4.5 V

15

ns

VIO Above 2.3 V

26

ns

1 See Figure 3 and Figure 4 for load conditions.

Rev. E | Page 5 of 28