AD1986 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD1986 Datasheet PDF : 52 Pages

| |||

Preliminary Technical Data

AD1986

PC BEEP (REGISTER 0x0A)

This controls the level of the Analog PC beep or the level and frequency of the Digital PC beep. The volume register contains four bits,

generating 16 volume steps of −3.0 dB each for a range of 0 dB to −45.0 dB. The tone frequency can be set between 47 Hz to 12,000 Hz or

disabled.

Per Intel’s BIOS writer’s guide, the PC beep signal should play via headphone out, line out, and mono out paths. BIOS algorithms should

unmute the PC beep register and the path to each output, and set the volume levels for playback.

When the AD1986 is in reset (the external RESET pin is low), the PCBEEP_IN pin is connected internally to all of the device output pins

(HEADPHONE L/R, LINE_OUT L/R, MONO_OUT, SURROUND L/R, and CENTER/LFE). There are no amplifiers or attenuators on

this path and the external circuitry connected to this pin should anticipate the drive requirements for the multiple output sources.

Headphones connected to output pins will substantially load the signal.

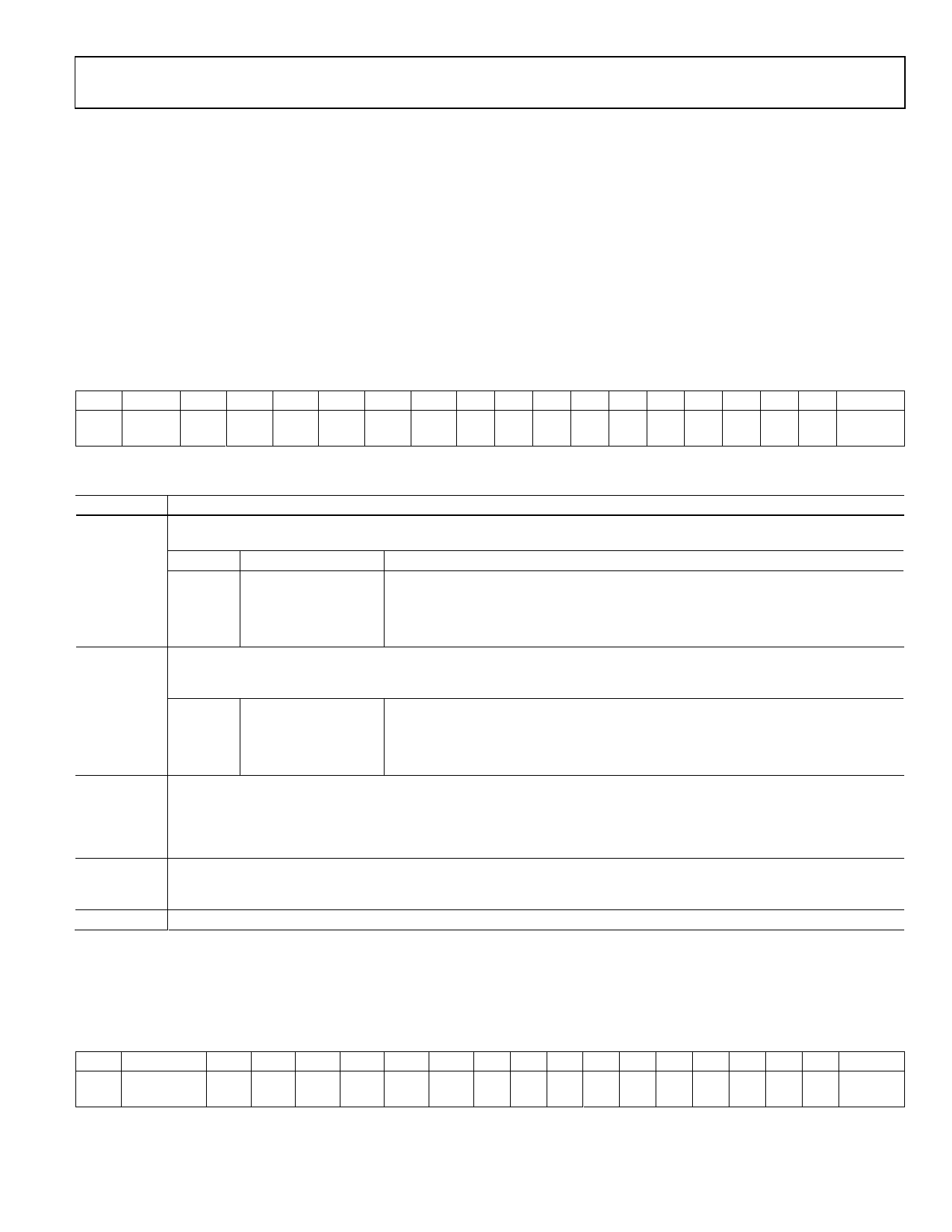

Reg Name D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

0x0A PC

M

Beep

A/DS x

F7 F6 F5 F4 F3 F2 F1 F0 V3 V2 V1 V0 x 0x8000

Table 34.

Register

V [3:0]

(Analog or

Digital

Volume)

Function

Controls the gain into the output mixer from 0 dB to −45.0 dB. The least significant bit represents −3.0 dB. The gain default

is 0 dB and muted.

M

V3...V0

Function

Default

0

0000

0 dB

Default

0

1111

−45 dB attenuation

1

xxxx

Muted

F [7:0]

(PC Beep

Frequency)

A/DS

(PC Beep

Source)

M

(PC Beep

Mute)

x

The result of dividing the 48 kHz clock by four times this number, allowing tones from 47 Hz to 12 kHz. A value of 0x00

disables internal PC beep generation. The digitally-generated signal is close to a square wave and is not intended to be a

high quality signal.

F7...F0

Function

0000

Disabled

Default

0001

12,000 Hz tone

1111

47 Hz tone

Selects either the digital PC beep generator (= 0) or analog PCBEEP pin (= 1). When the

CODEC is in reset mode the analog PCBEEP pin is routed to the outputs via a high

impedance path. Once ot of reset, this bit must be programmed to a 1 to pass through any

signals on the analog PCBEEP pin. Designers may choose not to connect the analog PCBEEP

pin and use the digital PC beep generator solely.

Default: digitally-selected

(0x0)

When this bit is set to 1, the PC beep signal (analog or digital) is muted.

Default: muted (0x1)

Reserved.

Default: 0

PHONE VOLUME (REGISTER 0x0C)

This register controls the PHONE_IN mute and gain to the analog mixer section. The volume register contains five bits, generating

32 volume steps of 1.5 dB each for a range of 12.0 dB to −34.5 dB. This does not control the record ADC gain (see Register 0x1C).

Reg Name

0x0C Phone

Volume

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

Mx

x

x

x

x

x x x x x V4 V3 V2 V1 V0 0x8008

Rev. 0 | Page 19 of 52