AD1836AASZ 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD1836AASZ Datasheet PDF : 24 Pages

| |||

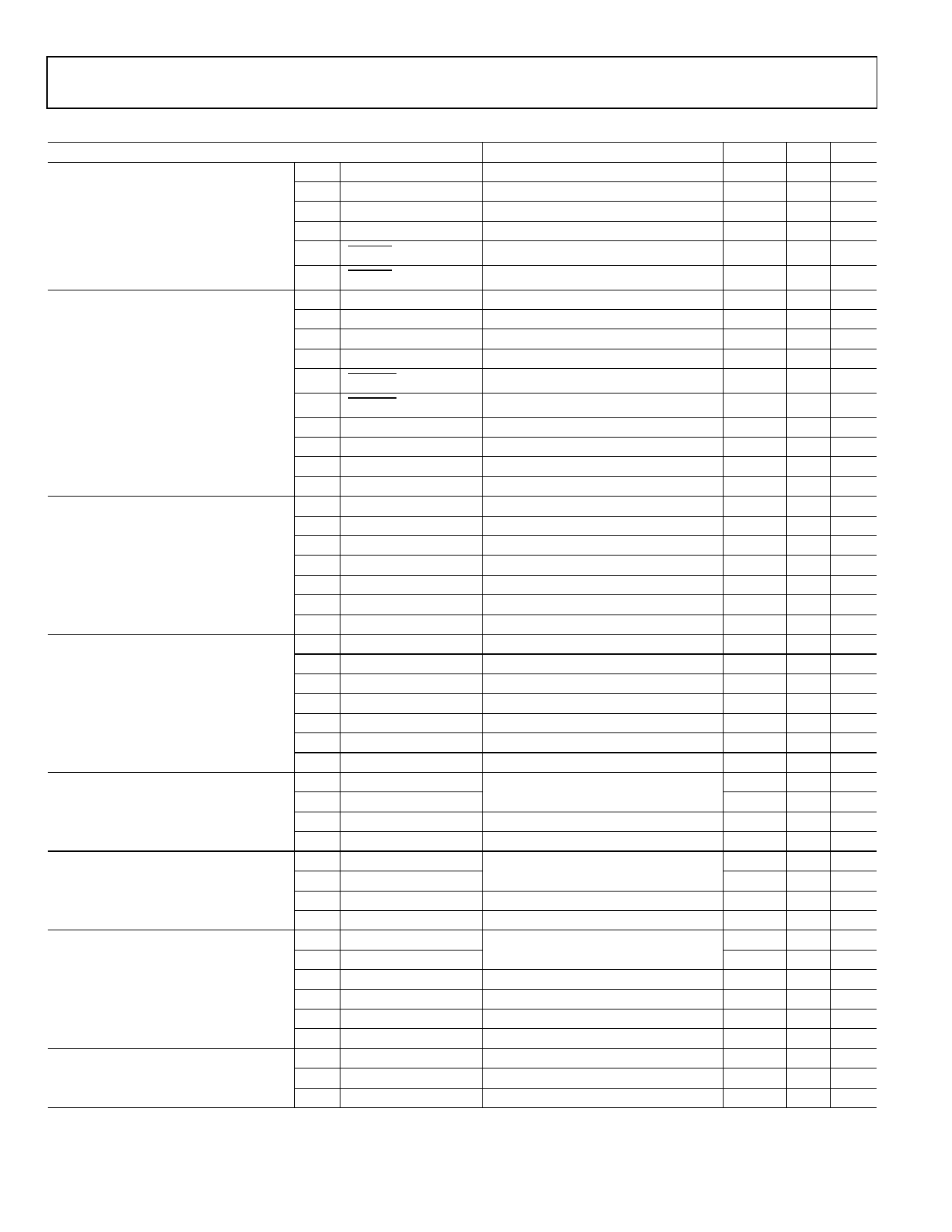

AD1836A

Table 7. Timing Specifications

Parameter

MASTER CLOCK AND RESET

SPI PORT

DAC SERIAL PORT

(Normal Modes)

DAC SERIAL PORT

(Packed 128 Mode, Packed 256 Mode)

ADC SERIAL PORT

(Normal Modes)

ADC SERIAL PORT

(Packed 128 Mode, Packed 256 Mode)

tMH

tML

tMCLK

fMCLK

MCLK High

MCLK Low

MCLK Period

MCLK Frequency

tPDR PD/RST Low

tPDRR PD/RST Recovery

tCHH CCLK High

tCHL CCLK Low

tCDS CDATA Setup

tCDH CDATA Hold

tCLS CLATCH Setup

tCLH CLATCH Hold

tCODE COUT Enable

tCOD COUT Delay

tCOH COUT Hold

tCOTS COUT Three-State

tDBH DBCLK High

tDBL DBCLK Low

fDB DBCLK Frequency

tDLS DLRCLK Setup

tDLH DLRCLK Hold

tDDS DSDATA Setup

tDDH DSDATA Hold

tDBH DBCLK High

tDBL DBCLK Low

fDB DBCLK Frequency

tDLS DLRCLK Setup

tDLH DLRCLK Hold

tDDS DSDATA Setup

tDDH DSDATA Hold

tABD ABCLK Delay

tALS

tABDD

tABD

LRCLK Skew

ASDATA Delay

ABCLK Delay

tALS

tABDD

tABD

LRCLK Skew

ASDATA Delay

ABCLK Delay

ADC SERIAL PORT

(TDM Packed AUX)

AUXILIARY INTERFACE

tALS

tABDD

tDDS

tDDH

tAXDS

tAXDH

tDXDD

LRCLK Skew

ASDATA Delay

DSDATA1 Hold

DSDATA1 Hold

AAUXDATA Setup

AAUXDATA Hold

DAUXDATA Delay

Data Sheet

Comments

512 × fS Mode

512 × fS Mode

512 × fS Mode

512 × fS Mode

Reset to Active Output

To CCLK Rising

From CCLK Rising

To CCLK Rising

From CCLK Falling

From CCLK Falling

From CCLK Falling

From CCLK Falling

From CCLK Falling

To DBCLK Rising

From DBCLK Rising

To DBCLK Rising

From DBCLK Rising

To DBCLK Rising

From DBCLK Rising

To DBCLK Rising

From DBCLK Rising

From MCLK Transition, 256 × fS Mode

From MCLK Rising, 512 × fS Mode

From ABCLK Falling

From ABCLK Falling

From MCLK Transition, 256 × fS Mode

From MCLK Rising, 512 × fS Mode

From ABCLK Falling

From ABCLK Falling

From MCLK Transition, 256 × fS Mode

From MCLK Rising, 512 × fS Mode

From ABCLK Falling

From ABCLK Falling

To ABCLK Rising

From ABCLK Rising

To AUXBCLK Rising

From AUXBCLK Rising

From AUXBCLK Falling

Min

Max Unit

18

ns

18

ns

36

ns

27 MHz

5

ns

4500

tMCLK

10

ns

10

ns

5

ns

5

ns

5

ns

5

ns

10 ns

10 ns

0

ns

10 ns

15

ns

15

ns

64 × fS

ns

0

ns

10

ns

0

ns

20

ns

15

ns

15

ns

256 × fS

ns

0

ns

10

ns

0

ns

20

ns

15 ns

–2

+2 ns

5

ns

15 ns

–2

+2 ns

5

ns

15 ns

–2

+2 ns

5

ns

0

ns

7

ns

7

ns

10

ns

25 ns

Rev. A | Page 6 of 24