MC54HCT74AJ 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

일치하는 목록

MC54HCT74AJ Datasheet PDF : 5 Pages

| |||

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Dual D Flip-Flop with

Set and Reset with LSTTL

Compatible Inputs

High–Performance Silicon–Gate CMOS

The MC74HCT74A is identical in pinout to the LS74. This device may be

used as a level converter for interfacing TTL or NMOS outputs to High Speed

CMOS inputs.

This device consists of two D flip–flops with individual Set, Reset, and

Clock inputs. Information at a D–input is transferred to the corresponding Q

output on the next positive going edge of the clock input. Both Q and Q

outputs are available from each flip–flop. The Set and Reset inputs are

asynchronous.

• Output Drive Capability: 10 LSTTL Loads

• TTL NMOS Compatible Input Levels

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 4.5 to 5.5 V

• Low Input Current: 1.0 µA

• In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

• Chip Complexity: 136 FETs or 34 Equivalent Gates

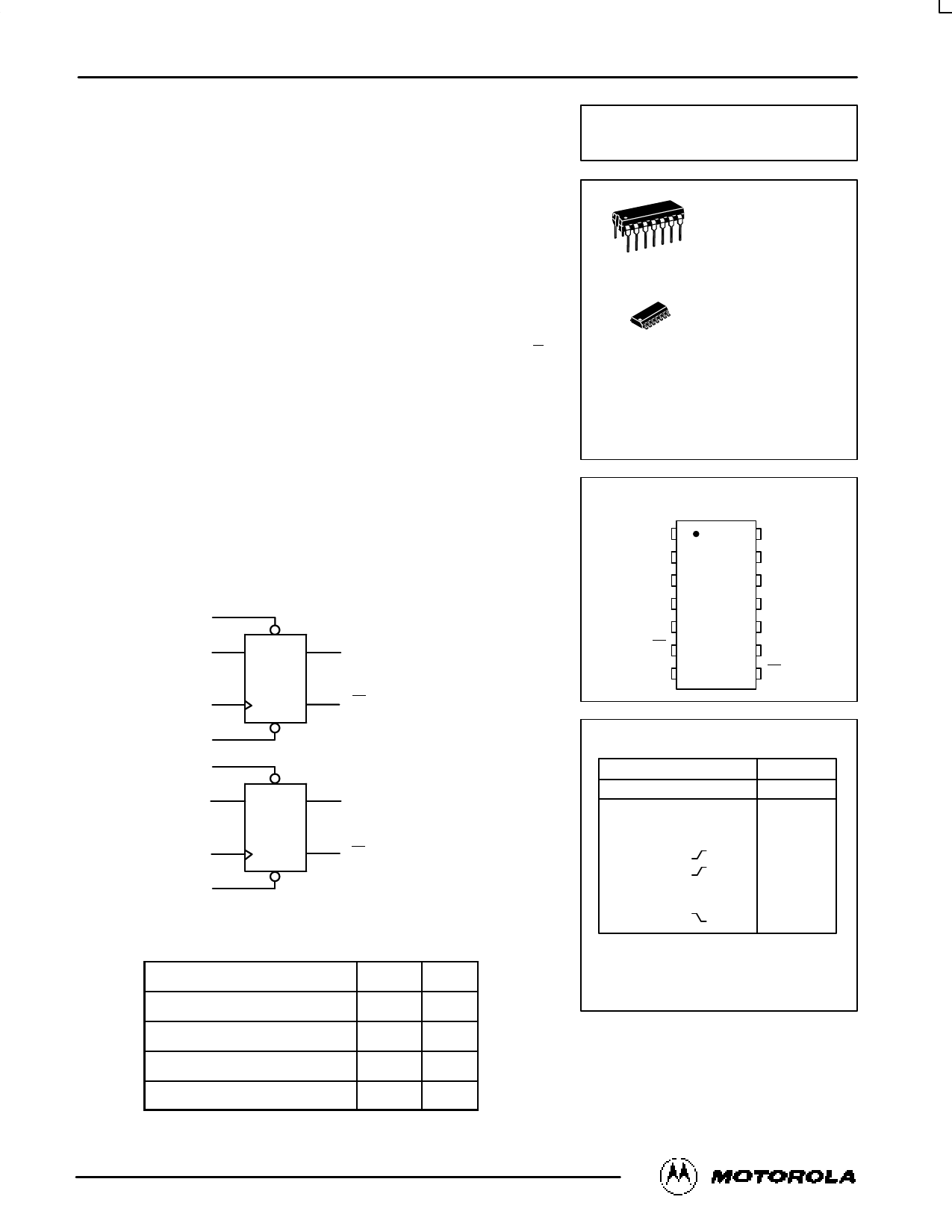

LOGIC DIAGRAM

RESET 1 1

DATA 1 2

5

Q1

3

CLOCK 1

SET 1 4

13

RESET 2

DATA 2 12

6

Q1

9

Q2

11

CLOCK 2

8

Q2

10

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ SET 2

PIN 14 = VCC

PIN 7 = GND

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Design Criteria

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Internal Gate Count*

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Internal Gate Propagation Delay

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Internal Gate Power Dissipation

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Speed Power Product

Value

34

1.5

5.0

.0075

Units

ea.

ns

µW

pJ

* Equivalent to a two–input NAND gate.

MC74HCT74A

14

1

N SUFFIX

PLASTIC PACKAGE

CASE 646–06

14

1

D SUFFIX

SOIC PACKAGE

CASE 751A–03

ORDERING INFORMATION

MC54HCTXXAJ

MC74HCTXXAN

MC74HCTXXAD

Ceramic

Plastic

SOIC

PIN ASSIGNMENT

RESET 1 1

DATA 1 2

CLOCK 1 3

SET 1 4

Q1 5

Q1 6

GND 7

14 VCC

13 RESET 2

12 DATA 2

11 CLOCK 2

10 SET 2

9 Q2

8 Q2

FUNCTION TABLE

Inputs

Set Reset Clock Data

LH

HL

LL

HH

HH

HH

HH

HH

XX

XX

XX

H

L

LX

HX

X

Outputs

QQ

HL

LH

H* H*

HL

LH

No Change

No Change

No Change

* Both outputs will remain high as long as

Set and Reset are low, but the output

states are unpredictable if Set and Reset

go high simultaneously.

10/95

© Motorola, Inc. 1995

1

REV 6