MC54HCT163A 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

일치하는 목록

MC54HCT163A Datasheet PDF : 12 Pages

| |||

MC54/74HCT161A MC54/74HCT163A

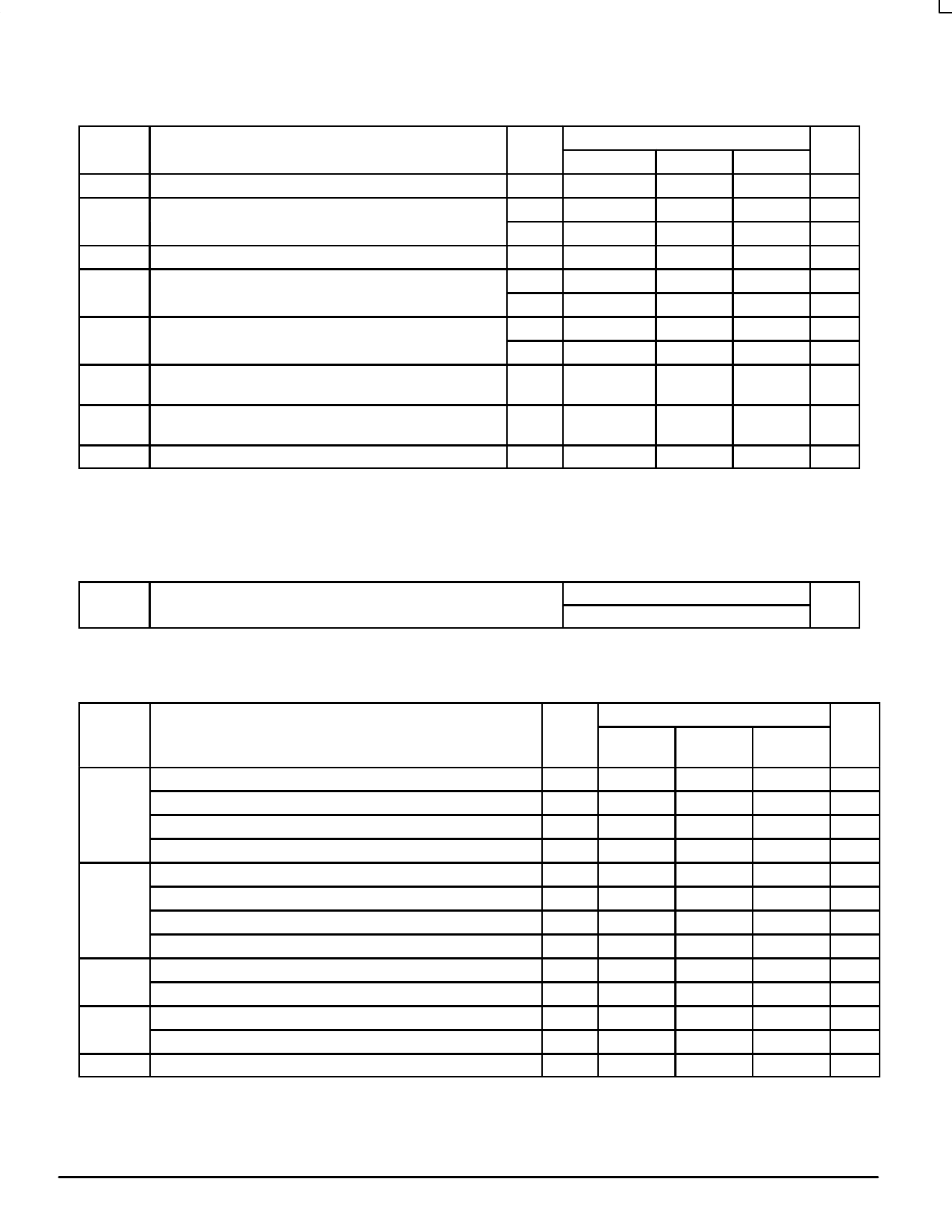

AC ELECTRICAL CHARACTERISTICS (VCC = 5.0 V ±10%: CL = 50 pF, Input tr = tf = 6.0 ns)

Guaranteed Limit

Symbol

Parameter

Fig

– 55 to 25_C

≤85°C

≤125°C Unit

fmax Maximum Clock Frequency (50% Duty Cycle)*

1,7

30

tPLH Maximum Propagation Delay Clock to Q

1,7

20

tPHL

1,7

25

tPHL Maximum Propagation Delay Reset to Q (HCT161A Only)

2,7

25

tPLH Maximum Propagation Delay Enable T to Ripple Carry Out

3,7

16

tPHL

3,7

21

tPLH Maximum Propagation Delay Clock to Ripple Carry Out

1,7

22

tPHL

1,7

28

tPHL

Maximum Propagation Delay Reset to Ripple Carry Out

(HCT161A Only)

2,7

24

24

20

MHz

23

28

ns

30

32

ns

29

33

ns

18

20

ns

24

28

ns

25

28

ns

33

35

ns

28

32

ns

tTLH,

tTHL

Cin

Maximum Output Transition Time, Any Output

Maximum Input Capacitance

2,7

15

1,7

10

19

22

ns

10

10

pF

* Applies to noncascaded/nonsynchronous clocked configurations only. With synchronously cascaded counters, (1) Clock to Ripple Carry Out

propagation delays, (2) Enable T or Enable P to Clock setup times, and (3) Clock to Enable T or Enable P hold times determine fmax. However,

if Ripple Carry Out of each stage is tied to the Clock of the next stage (nonsynchronously clocked), the fmax in the table above is applicable. See

Applications information in this data sheet.

NOTE: For propagation delays with loads other than 50 pF, and information on typical parametric values, see Chapter 2 of the Motorola High–

Speed CMOS Data Book (DL129/D).

Typical @ 25°C, VCC = 5.0 V

CPD Power Dissipation Capacitance (Per Gate)*

60

pF

* Used to determine the no–load dynamic power consumption: PD = CPD VCC2f + ICC VCC. For load considerations, see Chapter 2 of the

Motorola High–Speed CMOS Data Book (DL129/D).

TIMING REQUIREMENTS (VCC = 5.0 V ±10%: CL = 50 pF, Input tr = tf = 6.0 ns)

Symbol

Parameter

Fig.

tsu

Minimum Setup Time, Preset Data Inputs to Clock

5

Minimum Setup Time, Load to Clock

5

Minimum Setup Time, Reset to Clock

(HCT163A Only) 4

Minimum Setup Time, Enable T or Enable P to Clock

6

th

Minimum Hold Time, Clock to Preset Data Inputs

5

Minimum Hold Time, Clock to Load

5

Minimum Hold Time, Clock to Reset

(HCT163A Only) 4

Minimum Hold Time, Clock to En T or En P

6

trec

Minimum Recovery Time, Reset Inactive to Clock (HCT161A Only)

2

Minimum Recovery Time, Load Inactive to Clock

2

tw

Minimum Pulse Width, Clock

Minimum Pulse Width, Reset

1

(HCT161A Only) 1

tr, tf

Maximum Input Rise and Fall Times

Guaranteed Limit

– 55 to

25_C

≤85°C

≤125°C Unit

12

18

20

ns

12

18

20

ns

12

18

20

ns

12

18

20

ns

3

3

3

ns

3

3

3

ns

3

3

3

ns

3

3

3

ns

12

17

23

ns

12

17

23

ns

12

15

18

ns

12

15

18

ns

500

500

500

ns

High–Speed CMOS Logic Data

3

DL129 — Rev 6

MOTOROLA