MAS2901CE 데이터 시트보기 (PDF) - Zarlink Semiconductor Inc

부품명

상세내역

일치하는 목록

MAS2901CE Datasheet PDF : 13 Pages

| |||

MA2901

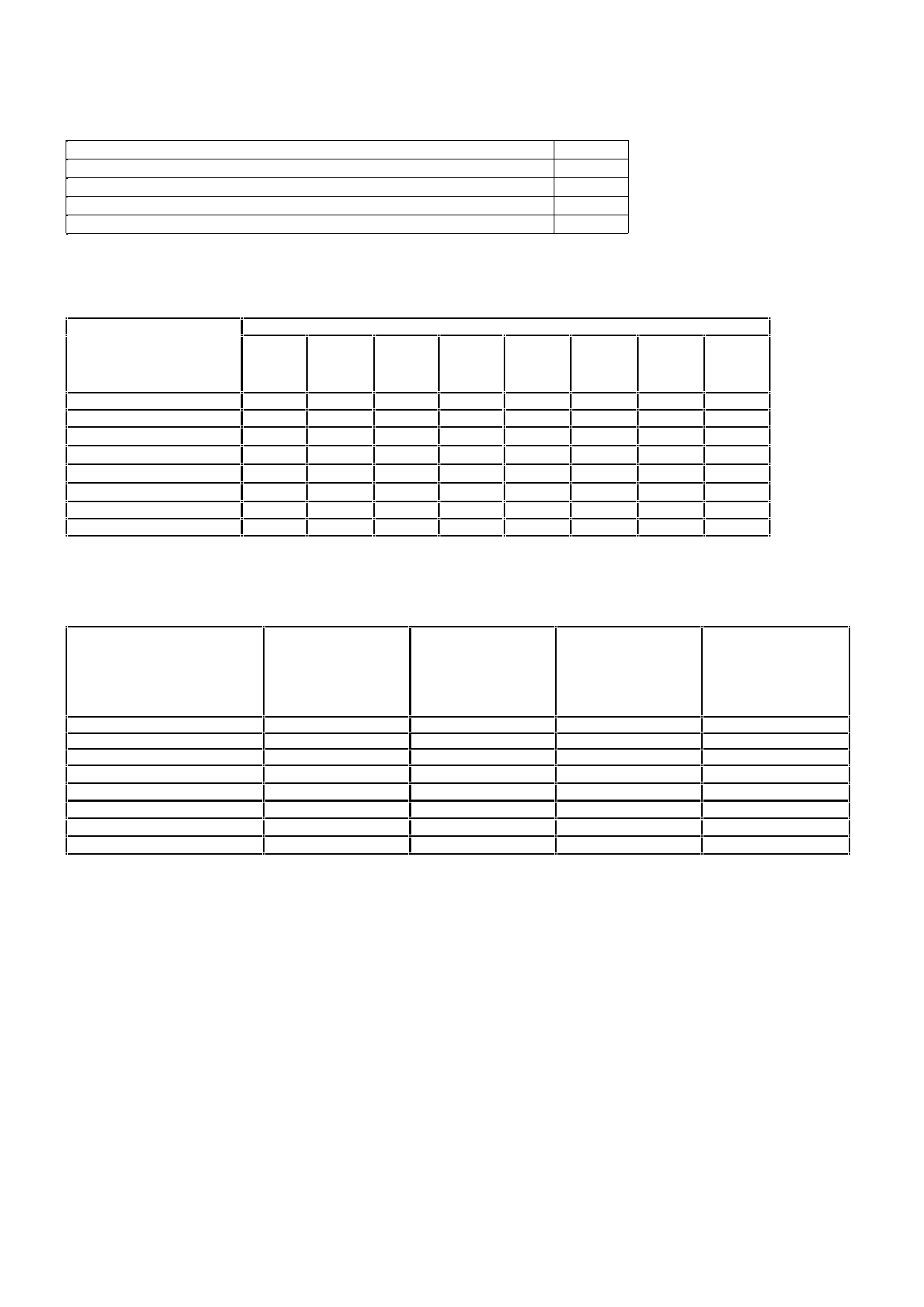

AC ELECTRICAL CHARACTERISTICS

Read-Modify-Write Cycle (from selection of A,B registers to end of a cycle 40ns

Maximum Clock Frequency to shift Q(50% duty cycle, I = 432 or 632)

25MHz

Minimum Clock LOW time

20ns

Minimum Clock HIGH time

20ns

Minimum Clock Period

40ns

Note: 1. These timings are applied during functional tests and are not routinely measured.

Figure 12: Cycle Time and Clock Characteristics

From Input

A,B Address

D

Cn

I0,1,2

I3,4,5

I6,7,8

A Bypass ALU(I=2xx)

Clock

Note: All timings in ns

To Output

Y

F3

Cn + 4 G,P

F=0

OVR RAM 0

Q0

RAM 3

Q3

65

55

60

55

70

65

65

-

55

40

50

50

65

55

55

-

60

40

35

-

55

35

50

-

70

50

55

55

70

55

65

-

60

45

50

45

65

50

65

-

45

-

-

-

-

-

30

30

45

-

-

-

-

-

-

-

55

50

55

50

50

55

55

35

Figure 13: Combinational Propagation Delays

Input

CP:

Set-up Time

Hold Time

Before H → L

After H → L

A,B Source Address

25

5

B Destination Address

25

No change

D

-

-

Cn

-

I0,1,2

-

I3,4,5

-

I6,7,8

10

RAM0,3, Q0,3

-

MIL-STD-883, method 5005, subgroups 9, 10, 11

-

-

-

No change

-

Note: 1. VDD = 5V ±10%, over full operational temperature range

2. CL = 50 pF

Set-up Time

Before L → H

30

No change

40

40

45

45

No change

15

Figure 14: Set-up and Hold Times Relative to Clock (CP) Input

Hold Time

After L → H

-

5

0

0

0

0

10

10

8