PDI1394L41 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

일치하는 목록

PDI1394L41 Datasheet PDF : 81 Pages

| |||

Philips Semiconductors

1394 content protection AV link layer controller

Preliminary specification

PDI1394L41

1.0 FEATURES

• IEEE1394.a and IEEE1394–1995 Standard Link Layer Controller

• Hardware Support for the IEC61883 International Standard of

Digital Interface for Consumer Electronics

• Interface to any IEEE 1394–1995 or 1394.a Physical Layer

Interface

• 5V Tolerant I/Os

• Single 3.3V supply voltage

• Full-duplex isochronous operation

• Operates with 400/200/100 Mbps physical layer devices

• 12K byte fully programmable FIFO pool for isochronous and

asynchronous data

• Supports single capacitor isolation mode and IEEE 1394–1995,

Annex J. isolation

• 6-field deep SYT buffer added to enhance real-time isochronous

synchronization using the AVFSYNC pin

• Generates its own AV port clocks under software control. Select

one of three frequencies: 24.576, 12.288, or 6.144 MHz

• Hardware support for the “5C” content protection method

• On chip timer resources

• Flexible 8/16 bit multiplexed/non-multiplexed host interface

• Parallel AV interface

• Fast 56-bit M6 cipher/decipher blocks capable of operating at over

80 Mbps

• Hardware authentication acceleration to reduce software

processor loading

• Highly configurable 12 K byte FIFO

2.0 DESCRIPTION

The PDI1394L41, Philips Semiconductors Full Duplex 1394

Audio/Video (AV) Link Layer Controller, is an IEEE 1394–1995

compliant link layer controller featuring 2 embedded AV layer

interfaces. The AV layers are designed to encrypt and pack, or

unpack and decrypt application data packets for transmission over

the IEEE1394 bus using isochronous data transfers and the “5C”

content protection method.

The application data is packetized according to the IEC 61883

International Standard of Interface for Consumer Electronic

Audio/Video Equipment. Both AV layer interfaces are byte-wide

ports capable of accommodating various MPEG–2 and DVC

codecs. A flexible host interface is provided for internal register

configuration as well as performing asynchronous data transfers.

Both 8 bit and 16 bit wide data paths, as well as

multiplexed/non-multiplexed access modes are supported.

The PDI1394L41 is powered by a single 3.3V power supply and the

inputs and outputs are 5V tolerant. It is available in the LQFP144

package.

2.1 Use restrictions

Due to rules set forth by the Digital Transmission Licensing

Administrator (DTLA) information concerning some features of the

L41 is the subject of a license issued by the DTLA. That information

has been omitted from this data sheet and is available only to DTLA

licensees on a restricted distribution basis. In order to obtain a copy

of the information, licensed parties should contact Philips

Semiconductors at 1394@philips.com and request data sheet

addendum AL41-1. Upon verification of the requestor’s DTLA

license status, a paper copy of the addendum will be sent to the

DTLA listed responsible person within the requesting company.

Distribution of samples and sales of the L41 chip are likewise

restricted to DTLA licensees. For information pertaining to the

procurement of a DTLA license please consult the DTLA website at

DTCP.com.

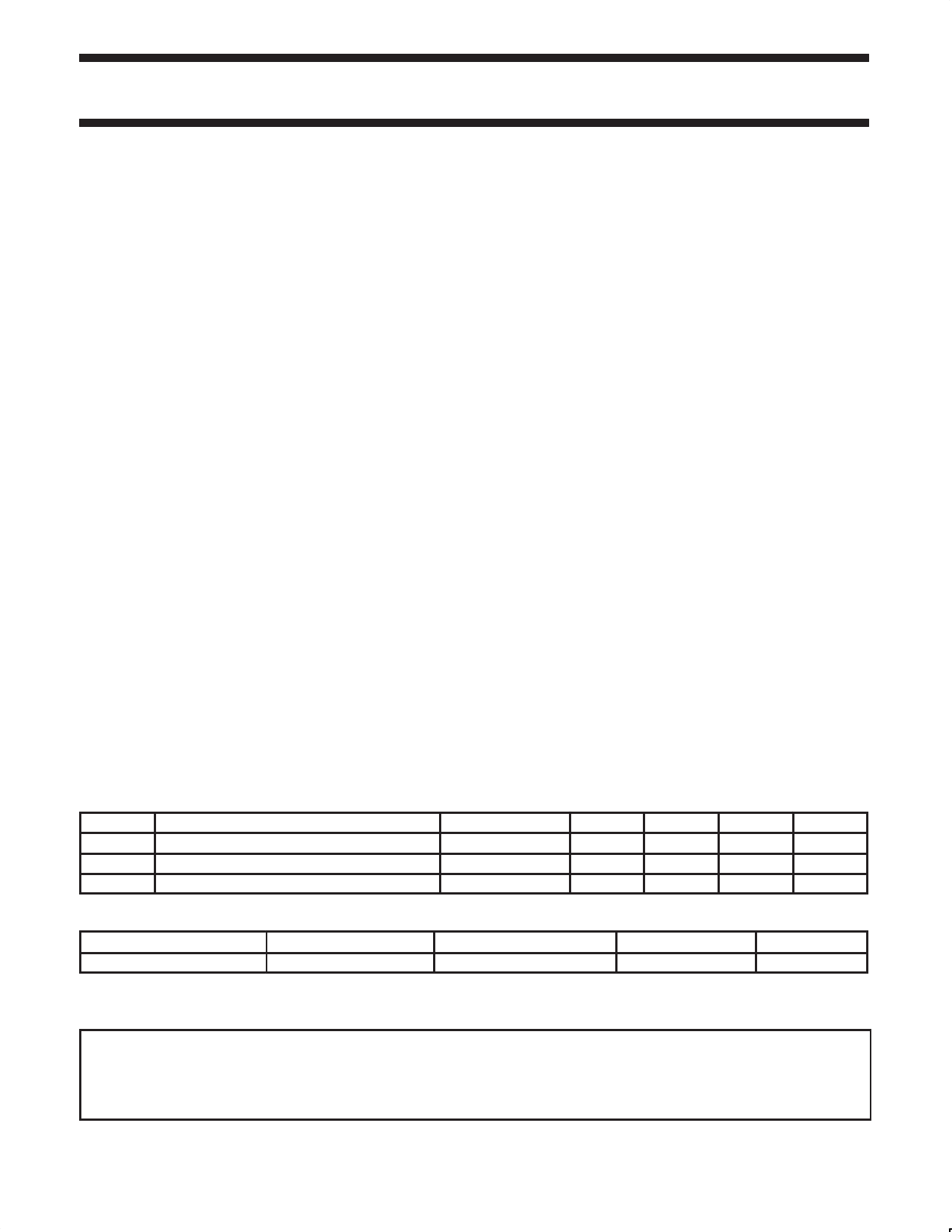

3.0 QUICK REFERENCE DATA

GND = 0V; Tamb = 25°C

SYMBOL

PARAMETER

VDD

Functional supply voltage range

IDD

Supply current @ VDD = 3.3V

SCLK

Device clock

CONDITIONS

Operating

MIN

3.0

49.147

TYP

3.3

110

49.152

MAX

3.6

150

49.157

UNIT

V

mA

MHz

4.0 ORDERING INFORMATION

PACKAGES

TEMPERATURE RANGE

144-pin LQFP144

0°C to +70°C

OUTSIDE NORTH AMERICA

PDI1394L41BE

NORTH AMERICA

PDI1394L41BE

PKG. DWG. #

SOT486–1

NOTE:

This datasheet is subject to change.

Please visit out internet website www.semiconductors.philips.com/1394 for latest changes.

2000 Apr 15

1