MT9122 데이터 시트보기 (PDF) - Mitel Networks

부품명

상세내역

일치하는 목록

MT9122 Datasheet PDF : 32 Pages

| |||

Preliminary Information

MT9122

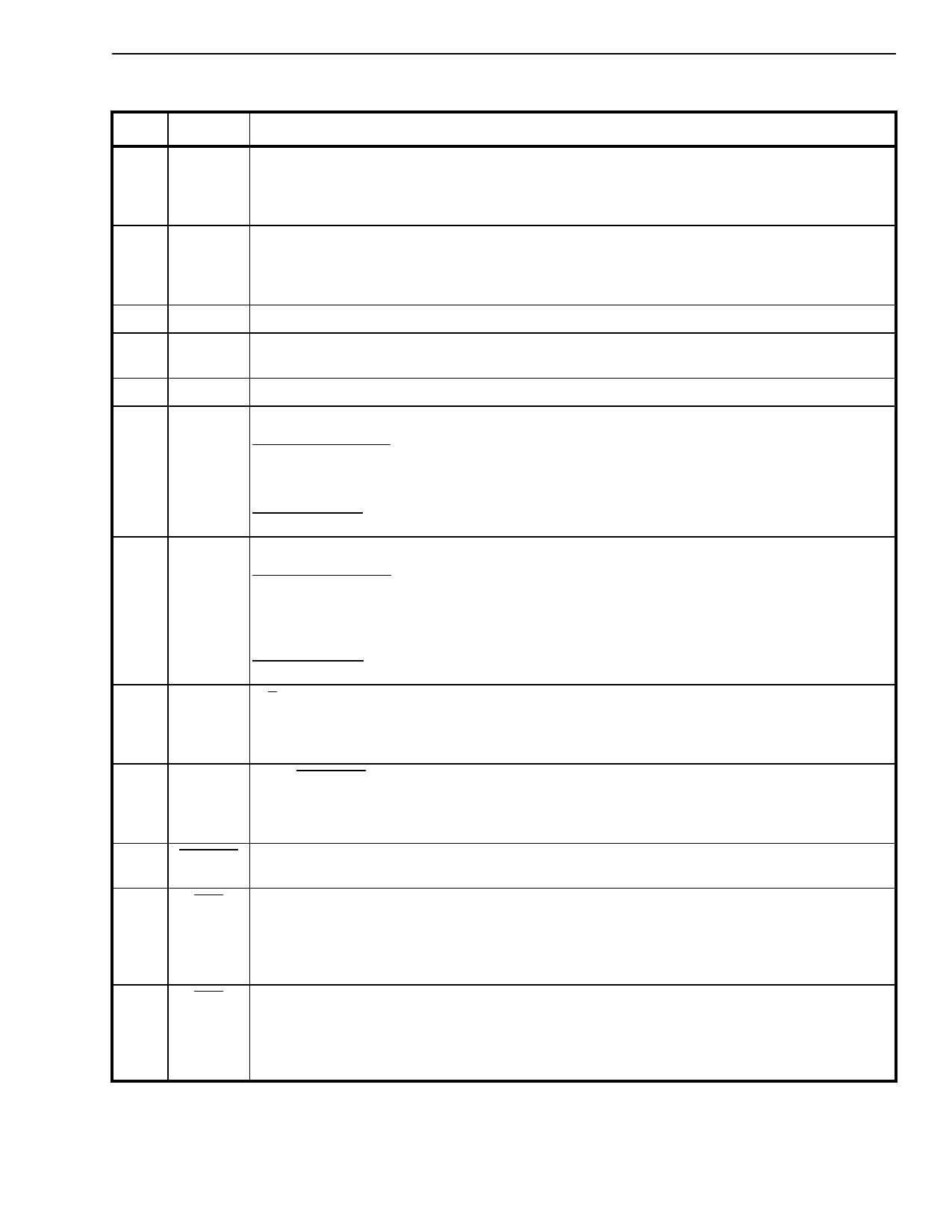

Pin Description (continued)

Pin #

5

6

7

8

9

10

Name

Description

Rin

Sin

VSS

MCLK

IC

NLP

Receive PCM Signal Input (Input). 128 kbit/s to 4096 kbit/s serial PCM input stream. Data

may be in either companded or 2’s complement linear format. Two PCM channels are time-

multiplexed on this pin. These are the Receive Input reference channels for Echo Cancellers

A and B. Data bits are clocked in following SSI or ST-BUS timing requirements.

Send PCM Signal Input (Input). 128 kbit/s to 4096 kbit/s serial PCM input stream. Data

may be in either companded or 2’s complement linear format. Two PCM channels are time-

multiplexed on this pin. These are the Send Input channels (after echo path) for Echo

Cancellers A and B. Data bits are clocked in following SSI or ST-BUS timing requirements.

Digital Ground: Nominally 0 volts.

Master Clock (Input): Nominal 20 MHz Master Clock input. May be connected to an

asynchronous (relative to frame signal) clock source.

Internal Connection (Input): Must be tied to Vss.

Non-Linear Processor Control (Input):

Controllerless Mode: An active high enables the Non-Linear Processors in Echo Cancellers A

and B. Both NLP’s are disabled when low. Intended for conformance testing to G.165 and it is

usually tied to Vdd for normal operation.

Controller Mode: This pin is ignored (tie to Vdd or Vss). The non-linear processor operation is

controlled by the NLPDis bit in Control Register 2. Refer to the Register Summary.

11

REV Reversal Detection (Input):

Controllerless Mode: An active high configures all the tone detectors to trigger only when a

2100Hz disable tone with periodic phase reversal is present (per G.165). When low, the tone

detectors will trigger upon detection of any 2100Hz disable tone, with or without periodic

phase reversal (per G.164).

Controller Mode: This pin is ignored (tie to VDD or VSS). The operation is controlled by the

PHDis bit in Control Register 2. Refer to the Register Summary.

12

LAW A/µ Law Select (Input):

An active low selects µ−Law companded PCM. When high, selects A-Law companded PCM.

This control is for both echo cancellers and is valid for both controller and controllerless

modes.

13 FORMAT ITU-T/Sign Mag (Input):

An active low selects sign-magnitude PCM code. When high, selects ITU-T (G.711) PCM

code. This control is for both echo cancellers and is valid for both controller and controllerless

modes.

14 PWRDN Power-down (Input): An active low resets the device and puts the MT9122 into a low-power

stand-by mode.

15

TD2 Tone Detect 2 (Output):

An active low output occurs when Echo Canceller B detects the presence of a valid 2100Hz

disabling tone (G.164 or G.165) on Rin or Sin pins. This output returns to a logic high once the

release criteria are met. The behavior of this pin is identical in both controller and

controllerless modes.

16

TD1 Tone Detect 1 (Output):

An active low output occurs when Echo Canceller A detects the presence of a valid 2100Hz

disabling tone (G.164 or G.165) on Rin or Sin pins. This output returns to a logic high once the

release criteria are met. The behavior of this pin is identical in both controller and

controllerless modes.

8-19