MT9122 데이터 시트보기 (PDF) - Mitel Networks

부품명

상세내역

일치하는 목록

MT9122 Datasheet PDF : 32 Pages

| |||

Preliminary Information

MT9122

Register Summary

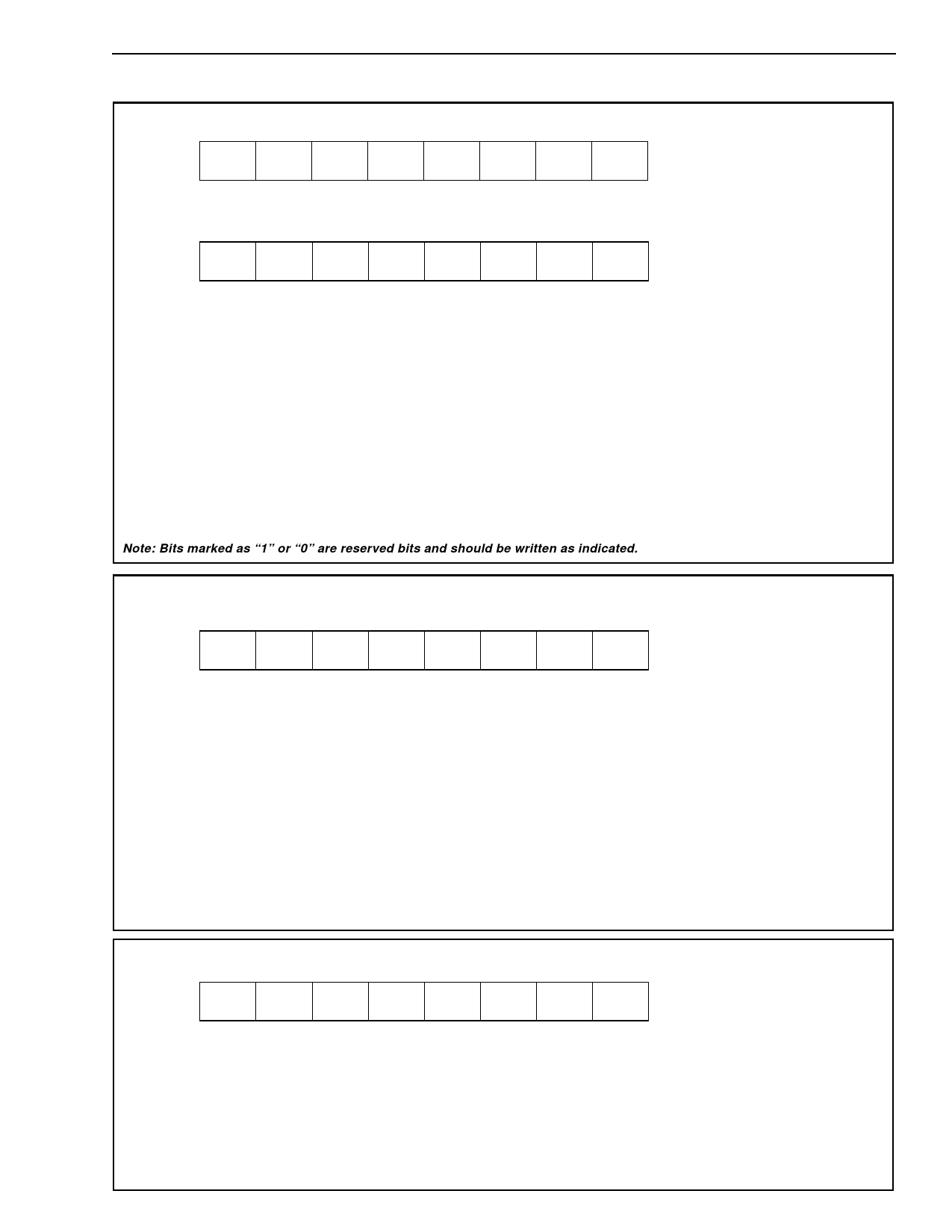

Echo Canceller A, Control Register 1

ADDRESS = 00h WRITE/READ VERIFY

CRA1

Reset INJDis BBM PAD Bypass AdaptDis

7

6

5

4

3

2

Echo Canceller B, Control Register 1

Extended

0 Delay

Power Reset Value

0000 0000

1

0

ADDRESS = 20h WRITE/READ VERIFY

CRB1

Extended-

Delay

AdaptDis

Bypass

PAD

BBM

INJDis

Reset

Reset INJDis BBM PAD Bypass AdaptDis 1

0

Power Reset Value

0000 0010

7

6

5

4

3

2

1

0

When high, Echo Cancellers A and B are internally cascaded into one 128ms echo canceller.

When low, Echo Cancellers A and B operate independently.

Do not enable both Extended-Delay and BBM configurations at the same time.

When high, echo canceller adaptation is disabled.

When low, the echo canceller dynamically adapts to the echo path characteristics.

When high, Sin data is by-passed to Sout and Rin data is by-passed to Rout.

When low, output data on both Sout and Rout is a function of the echo canceller algorithm.

When high, 12dB of attenuation is inserted into the Rin to Rout path.

When low the Rin to Rout path gain is 0dB.

When high the Back to Back configuration is enabled.

When low the Normal configuration is enabled. Do not enable Extended-Delay and BBM configurations at the same time.

Always set both BBM bits of the two echo cancellers to the same logic value to avoid conflict.

When high, the noise injection process is disabled. When low noise injection is enabled.

When high, the power-up initialization is executed presetting all register bits including this bit.

Note: Bits marked as “1” or “0” are reserved bits and should be written as indicated.

Echo Canceller A, Control Register 2

Echo Canceller B, Control Register 2

ADDRESS = 01h WRITE/READ VERIFY

ADDRESS = 21h WRITE/READ VERIFY

CR2

MuteR

MuteS

HPFDis

NBDis

AutoTD

NLPDis

PHDis

TDis

TDis PHDis NLPDis AutoTD NBDis HPFDis MuteS MuteR

Power Reset Value

0000 0000

7

6

5

4

3

2

1

0

When high, data on Rout is muted to quiet code. When low, Rout carries active code.

When high, data on Sout is muted to quiet code. When low, Sout carries active code.

When high, the offset nulling high pass filters are bypassed in the Rin and Sin paths.

When low, the offset nulling filters are active and will remove DC offsets on PCM input signals.

When high, the narrow-band detector is disabled. When low, the narrow-band detector is enabled.

When high, the echo canceller is in Bypass mode when the tone detectors detect the presence of 2100Hz tones. See PHDis

for qualification of 2100Hz tones.

When low, the echo canceller algorithm will remain operational regardless of the state of the 2100Hz tone detectors.

When high, the non-linear processor is disabled.

When low, the non-linear processors function normally. Useful for G.165 conformance testing.

When high, the tone detectors will trigger upon the presence of a 2100Hz tone regardless of the presence/absence of periodic

phase reversals.

When low, the tone detectors will trigger only upon the presence of a 2100Hz tone with periodic phase reversals.

When high, tone detection is disabled entirely. When low, tone detection is enabled.

Echo Canceller A, Status Register

Echo Canceller B, Status Register

ADDRESS = 02h READ

ADDRESS = 22h READ

SR

NB

TDG

Active

Down

Conv

DTDet

TD

TD DTDet Conv Down Active TDG

NB

Power Reset Value

0000 0000

7

6

5

4

3

2

1

0

Logic high indicates the presence of a narrow-band signal on Rin.

Tone detection status bit gated with the AutoTD bit.

Logic high indicates that AutoTD has been enabled and the tone detector has detected the presence of a 2100Hz tone.

Logic high indicates that the power level on Rin is above the threshold level (i.e., low power condition).

Decision indicator for the non-linear processor gain adjustment.

Decision indicator for rapid adaptation convergence. Logic high indicates a rapid convergence state.

Logic high indicates the presence of a double-talk condition.

Logic high indicates the presence of a 2100Hz tone.

8-33