HSP9501(2004) 데이터 시트보기 (PDF) - Intersil

부품명

상세내역

일치하는 목록

HSP9501 Datasheet PDF : 8 Pages

| |||

HSP9501

Functional Description

The HSP9501 is a 10-bit wide programmable length data

buffer. The length of delay is programmable from 2 to 1281

delays in single delay increments.

Data into the delay line may be selected from the data input

bus (DI0-9) or as recirculated output, depending on the state

of the mode select (MODSEL) control input.

Mode Select

The MODSEL control pin selects the source of the data

moving into the delay line. When MODSEL is low, the data

input bus (DI0-9) is the source of the data. When MODSEL

is high, the output of the HSP9501 is routed back to the input

to form a circular buffer.

The MODSEL control line is latched at the input by the CLK

signal. The edge which latches this control signal is deter-

mined by the CLKSEL control line. In either case, the

MODSEL line is latched on one edge of the CLK signal with

the following edge moving data into and through the

HSP9501. Refer to the functional timing waveforms for

specific timing references.

Clock Select Logic

The clock select logic is provided to allow the use of positive

or negative edge system clocks. The active edge of the CLK

input to the HSP9501 is controlled through the use of the

CLKSEL input.

When CLKSEL is low, the negative going edge of CLK is

used to control all internal operations. A high on CLKSEL

selects the positive going edge of CLK.

All synchronous timing (i.e., setup, hold and output

propagation delay times are relative to the CLK edge

selected by CLKSEL. Functional timing waveforms for each

state of CLKSEL are provided (refer to Timing Waveforms

for details).

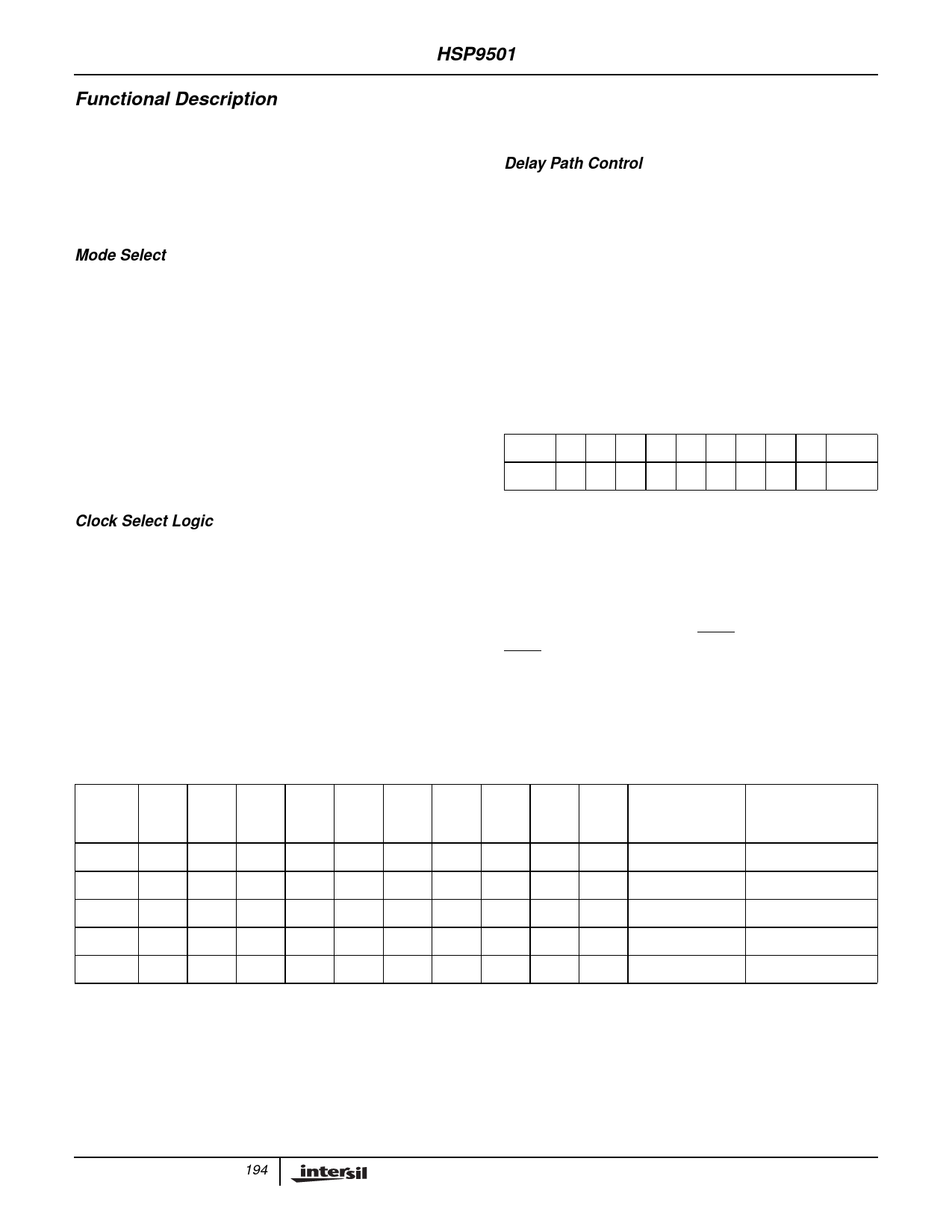

Delay Path Control

The HSP9501 buffer length is programmable from 2 to 1281

data words in one word increments. The minimum number of

delays which can be programmed is two, consisting of the

input and Output Buffer Registers only.

The length control inputs (LC0-10) are used to set the length

of the programmable delay ram which can vary in length

from 0 to 1279. The total length of the HSP9501 data buffer

will then be equal to the programmed value on LC0-10 plus

2. The programmed delay is established by the 11-bit integer

value of the LC0-10 inputs with LC-10 as the MSB and LC0

as the LSB.

For example,

LC10 9 8 7 6 5 4 3 2 1 LC0

0

000100000

1

programs a length value of 26 + 20 = 65. The total length of

the delay will be 65 + 2 or 67 delays.

Table 1 indicates several programming values. The decimal

value placed on LC0-10 must not exceed 1279. Controlled

operation with larger values is not guaranteed.

Values on LC0-10 are latched on the CLK edge selected by

the CLKSEL control line, when LCEN is active. LC0-10 and

LCEN must meet the specified setup and hold times relative

to the selected CLK edge for proper device operation.

TABLE 1. LENGTH CONTROL PROGRAMMING EXAMPLES

LC9 LS8 LC7 LC6 LC5 LC4 LC3 LC2 LC1 LC0 PROGRAMMED

LC10 210 29

28

27

26

25

24

23

22

21

20

LENGTH

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

1

1

0

118

0

1

1

0

0

1

0

1

0

0

0

808

1

0

0

0

0

0

1

1

0

0

1

1049

1

0

0

1

1

1

1

1

1

1

1

1279

TOTAL

LENGTH

N

2

120

810

1051

1281

4