HCF4035B 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

일치하는 목록

HCF4035B Datasheet PDF : 11 Pages

| |||

HCF4035B

4 STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER

s 4 STAGE CLOCKED SHIFT OPERATION

s SYNCHRONOUS PARALLEL ENTRY ON

ALL 4 STAGES

s JK INPUTS ON FIRST STAGE

s ASYNCHRONOUS TRUE/COMPLEMENT

CONTROL ON ALL OUTPUTS

s STATIC FLIP-FLOP OPERATION;

MASTER-SLAVE CONFIGURATION

s BUFFERED INPUTS AND OUTPUTS

s HIGH SPEED 12MHz (Typ.) at VDD = 10V

s QUIESCENT CURRENT SPECIF. UP TO 20V

s STANDARDIZED SYMMETRICAL OUTPUT

CHARACTERISTICS

s 5V, 10V AND 15V PARAMETRIC RATINGS

s INPUT LEAKAGE CURRENT

II = 100nA (MAX) AT VDD = 18V TA = 25°C

s 100% TESTED FOR QUIESCENT CURRENT

s MEETS ALL REQUIREMENTS OF JEDEC

JESD13B " STANDARD SPECIFICATIONS

FOR DESCRIPTION OF B SERIES CMOS

DEVICES"

DESCRIPTION

The HCF4035B is a monolithic integrated circuit

fabricated in Metal Oxide Semiconductor

technology available in DIP and SOP packages.

This device is a four stage clocked signal serial

register with provision for synchronous

PARALLEL inputs to each stage and SERIAL

inputs to the first stage via JK logic. Register

stages 2, 3, and 4 are coupled in a serial D flip-flop

configuration when the register is in the serial

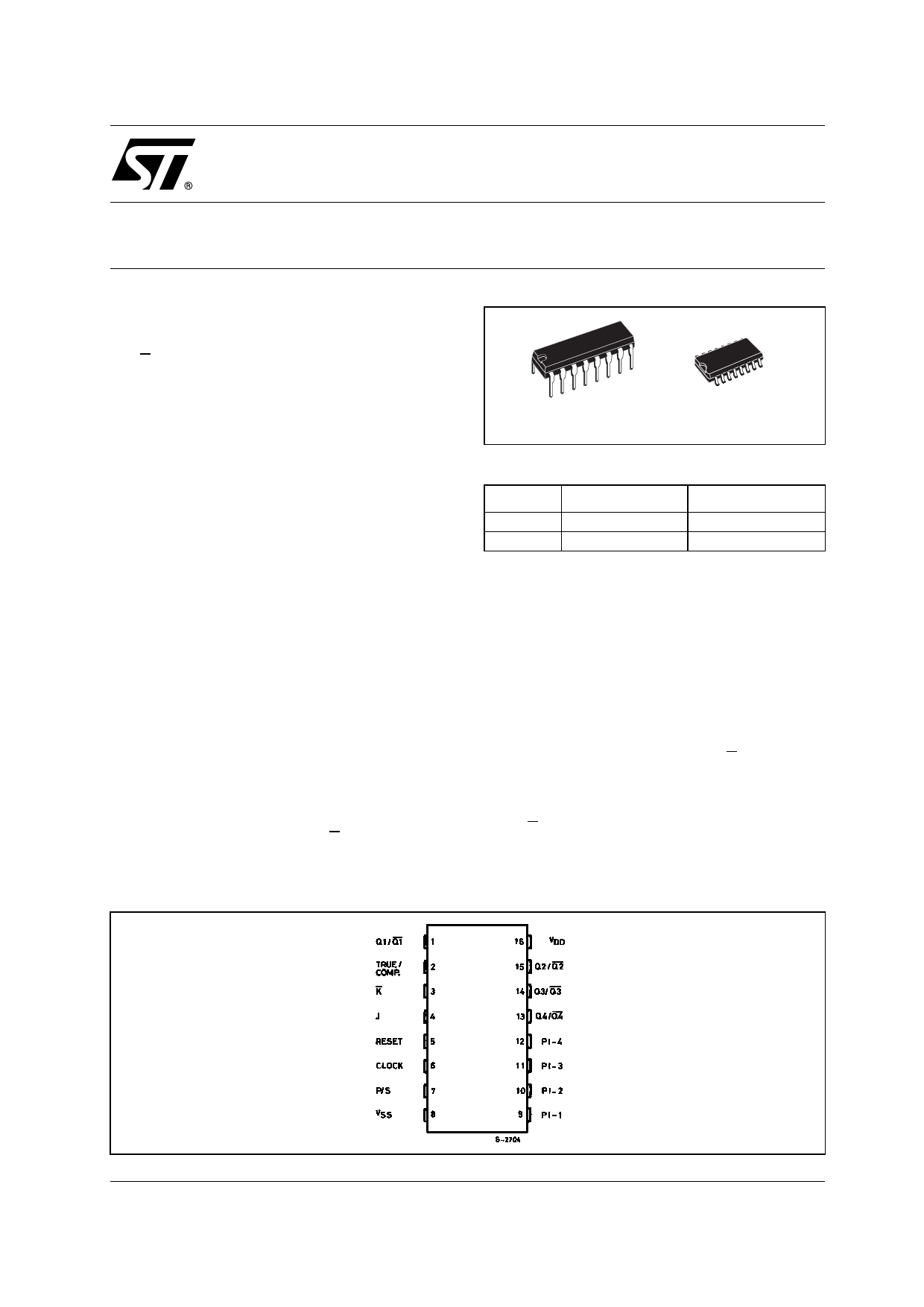

PIN CONNECTION

DIP

SOP

ORDER CODES

PACKAGE

TUBE

DIP

SOP

HCF4035BEY

HCF4035BM1

T&R

HCF4035M013TR

mode (PARALLEL/SERIAL control low). Parallel

entry into each register stage is permitted when

the PARALLEL/SERIAL control is high. In the

parallel or serial mode information is transferred

on positive clock transitions. When the TRUE/

COMPLEMENT control is high, the true contents

of the register are available at the output

terminals. When the TRUE/COMPLEMENT

control is low, the outputs are the complements of

the data in the register. The TRUE/

COMPLEMENT control functions asynchronously

with respect to the CLOCK signal. JK input logic is

provided on the first stage SERIAL input to

minimize logic requirements particularly in

counting and sequence generation applications.

With JK inputs connected together, the first stage

becomes a D flip-flop. An asynchronous common

RESET is also provided.

September 2001

1/11