LMU112 데이터 시트보기 (PDF) - LOGIC Devices

부품명

상세내역

일치하는 목록

LMU112 Datasheet PDF : 6 Pages

| |||

DEVICES INCORPORATED

LMU112

12 x 12-bit Parallel Multiplier

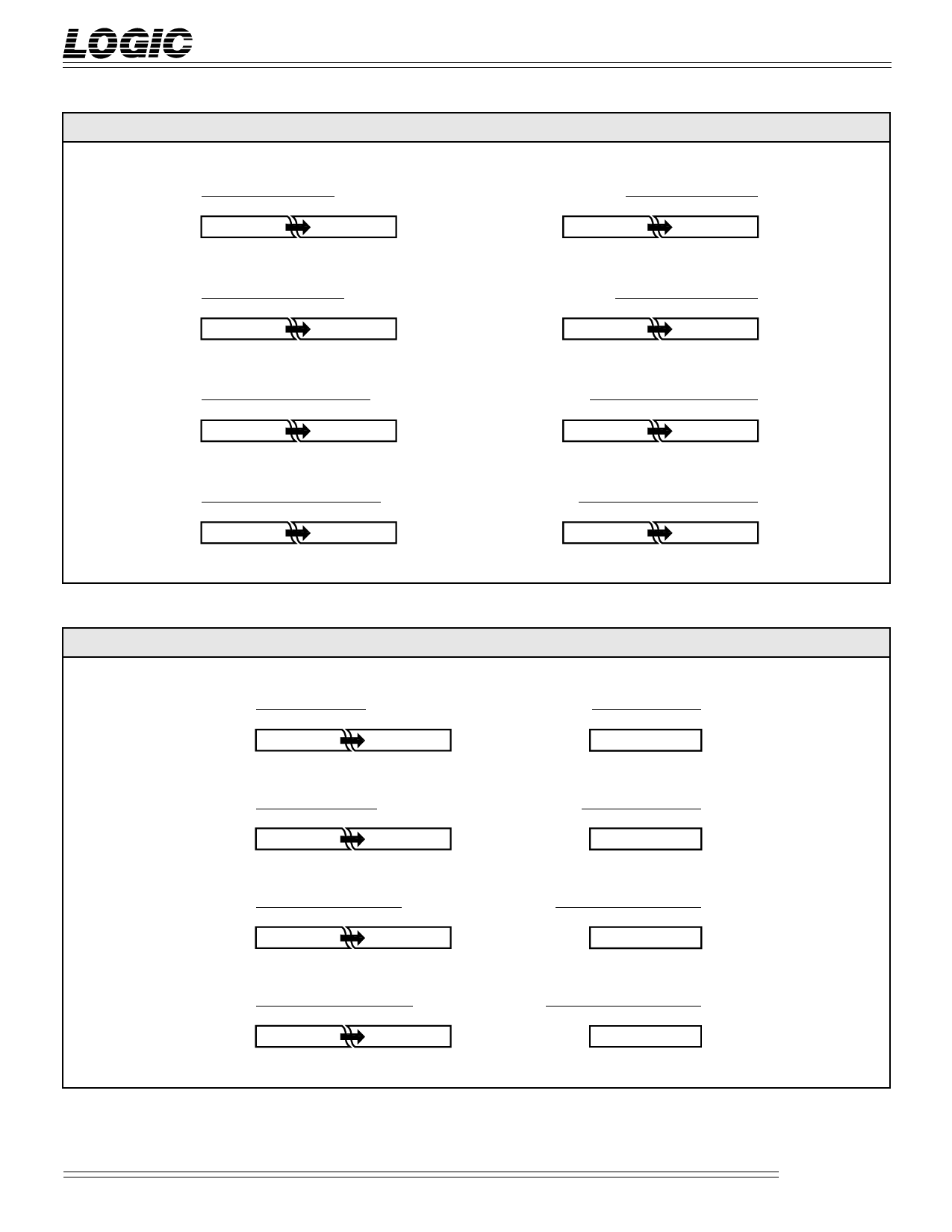

FIGURE 1A. INPUT FORMATS

AIN

BIN

Fractional Two’s Complement (TC = 1)

11 10 9

–20 2–1 2–2

(Sign)

210

2–9 2–10 2–11

11 10 9

–20 2–1 2–2

(Sign)

210

2–9 2–10 2–11

11 10 9

–211 210 29

(Sign)

Integer Two’s Complement (TC = 1)

210

22 21 20

11 10 9

–211 210 29

(Sign)

210

22 21 20

11 10 9

2–1 2–2 2–3

Unsigned Fractional (TC = 0)

210

2–10 2–11 2–12

11 10 9

2–1 2–2 2–3

210

2–10 2–11 2–12

11 10 9

211 210 29

Unsigned Integer (TC = 0)

210

22 21 20

11 10 9

211 210 29

210

22 21 20

FIGURE 1B. OUTPUT FORMATS

MSP

LSP

Fractional Two’s Complement

23 22 21

–20 2–1 2–2

(Sign)

14 13 12

2–9 2–10 2–11

11 10 9 8

2–12 2–13 2–14 2–15

23 22 21

–222 221 220

(Sign)

Integer Two’s Complement

14 13 12

213 212 211

11 10 9 8

210 29 28 27

Unsigned Fractional

23 22 21

2–1 2–2 2–3

14 13 12

2–10 2–11 2–12

11 10 9 8

2–13 2–14 2–15 2–16

23 22 21

223 222 221

Unsigned Integer

14 13 12

214 213 212

11 10 9 8

211 210 29 28

Multipliers

2

08/16/2000–LDS.112-K